### **COMPUTER ORGANIZATION**

#### I B.TECH II SEM FOR

CSE

(JNTUK)

(R20)

# HUMANITIES & BASIC SCIENCES DEPARTMENT

# V S M COLLEGE OF ENGINEERING

# RAMCHANDRAPURAM

E.G. Dt. - 533255

# **VSM COLLEGE OF ENGINEERING**

#### RAMACHANDRAPURAM

#### **1-2 Semester**

#### **COMPUTER ORGANIZATION**

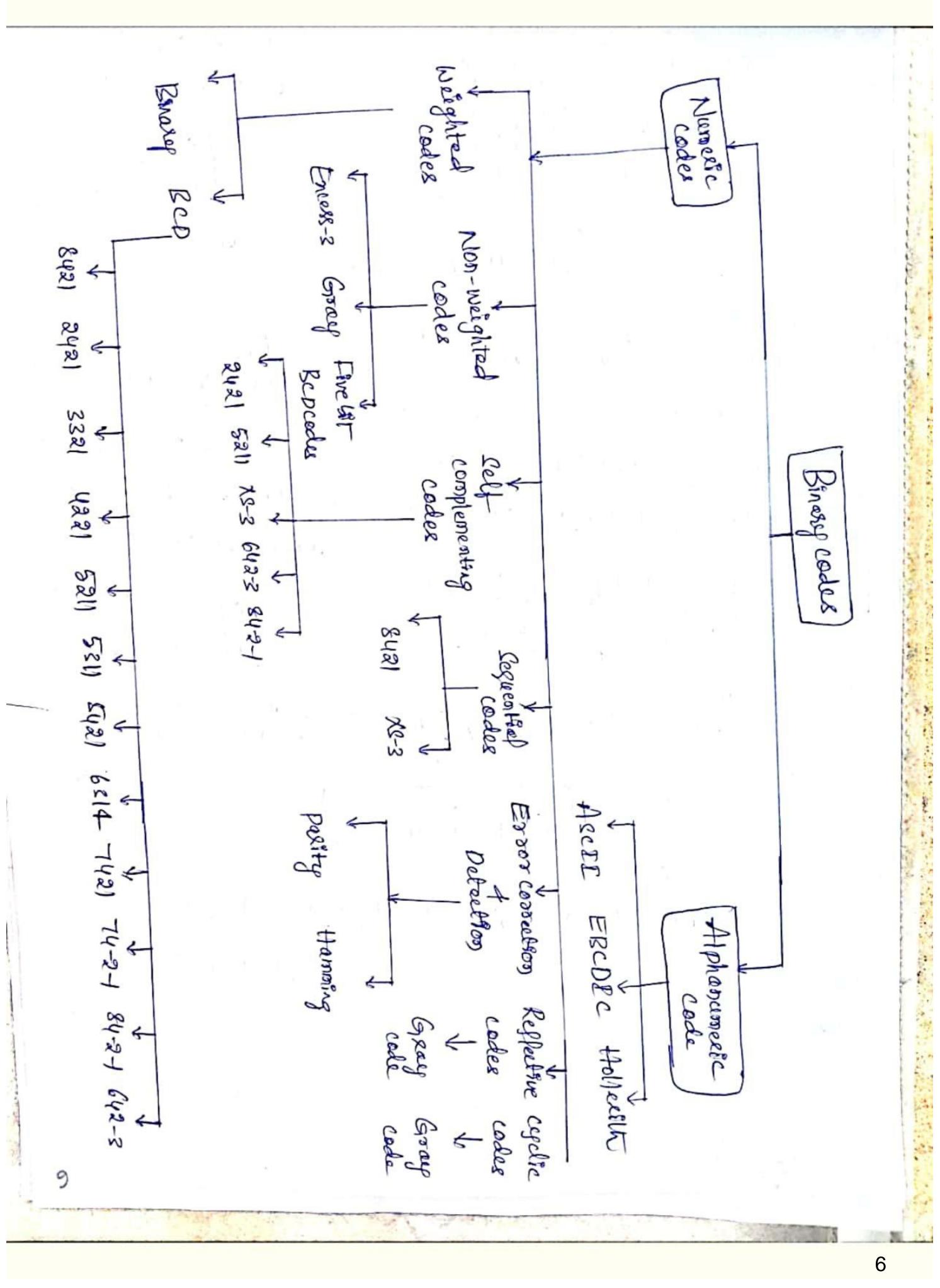

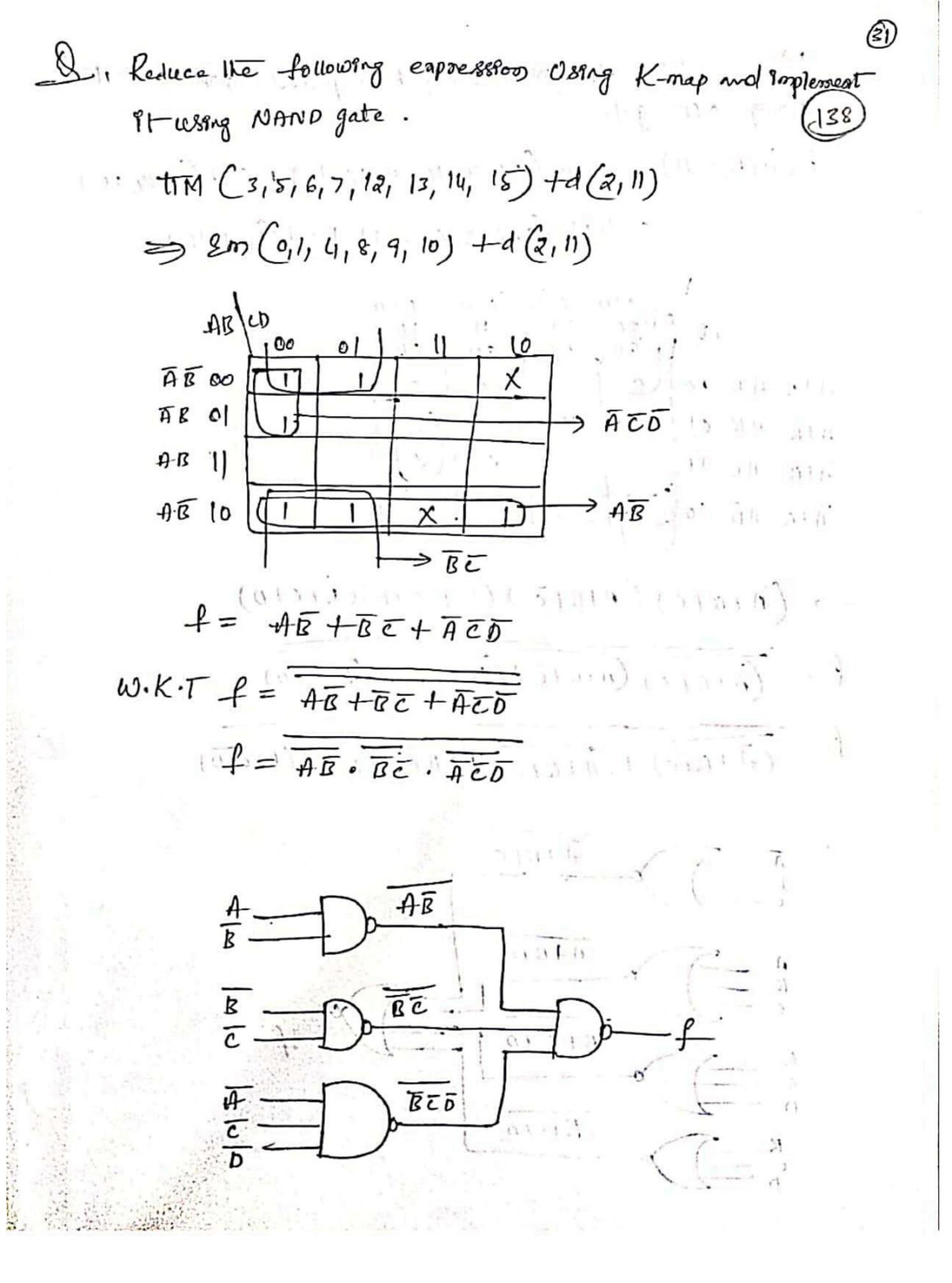

**UNIT I:** Digital Computers and Data Representation: Introduction ,Numbering Systems, Decimal to Binary Conversion, Binary Coded Decimal Numbers, Weighted Codes, Self Complementing Codes, Cyclic Codes, Error Detecting Codes, Error Correcting Codes, Hamming Code for Error Correction, Alphanumeric Codes, ASCI Code Data Representation: Data types, Complements, Fixed Point Representation, Floating Point Representation. Boolean Algebra and Logical gates: Boolean Algebra :Theorems and properties, Boolean functions, canonical and standard forms , minimization of Boolean functions using algebraic identities; Karnaugh map representation and minimization using two and three variable Maps ;Logical gates ,universal gates and Two-level realizations using gates : AND-OR, OR-AND, NAND-NAND and NOR-NOR structures.

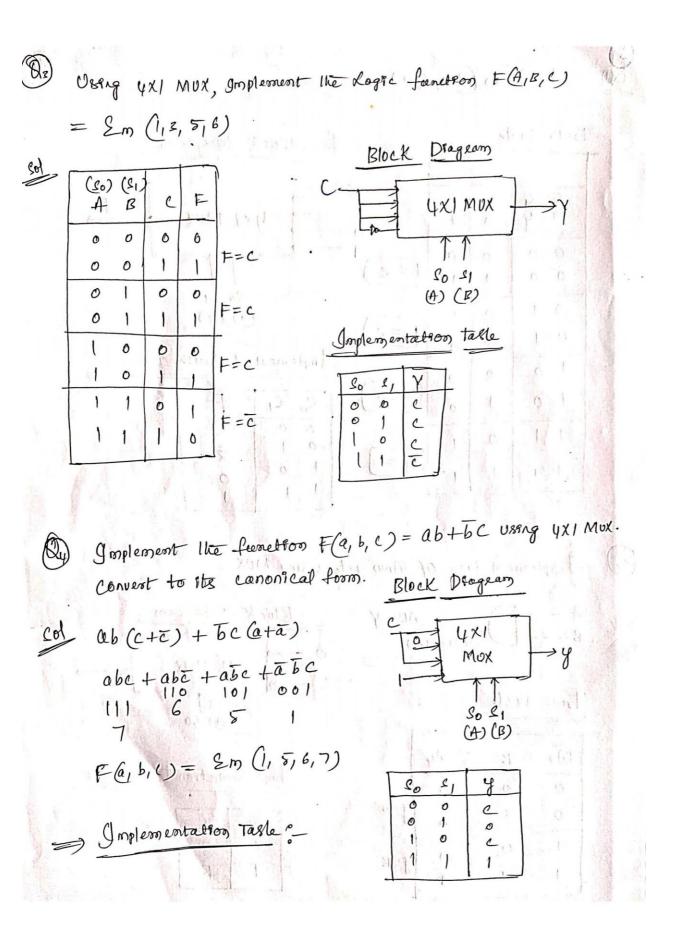

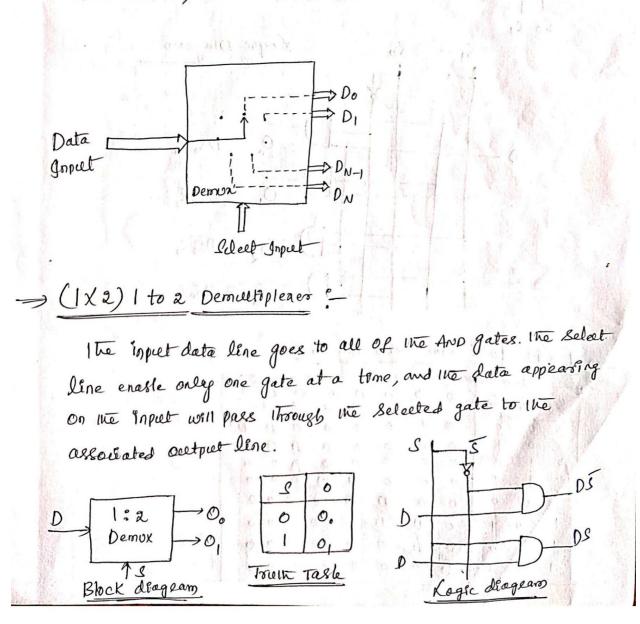

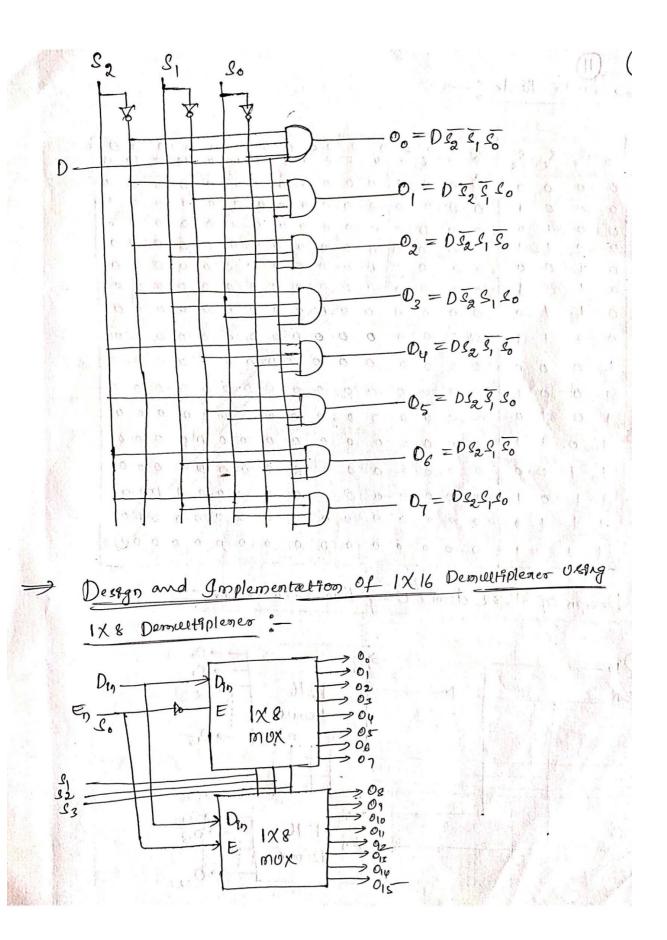

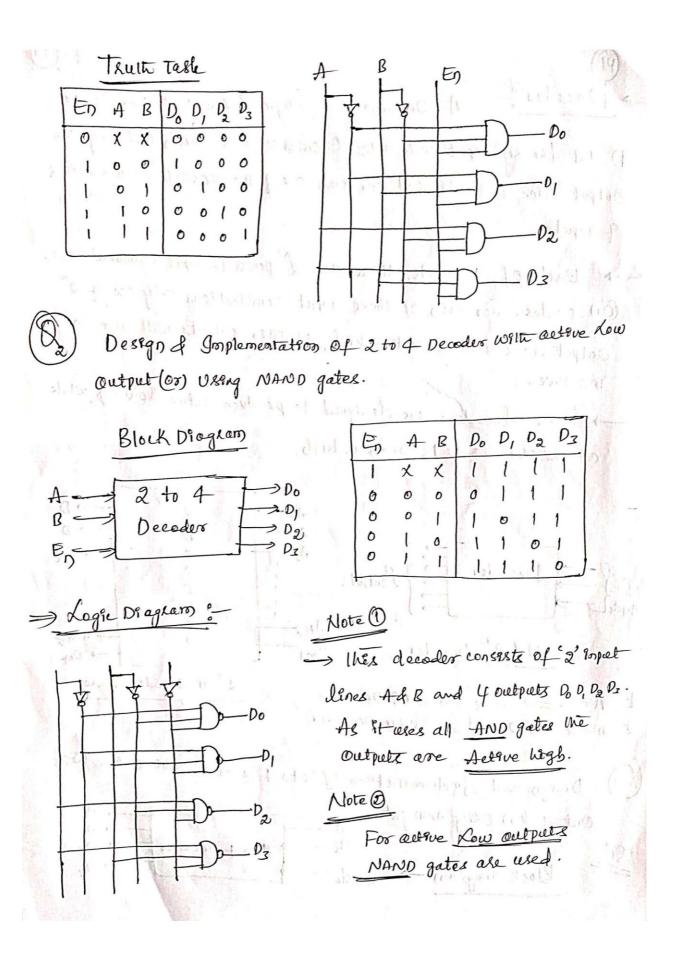

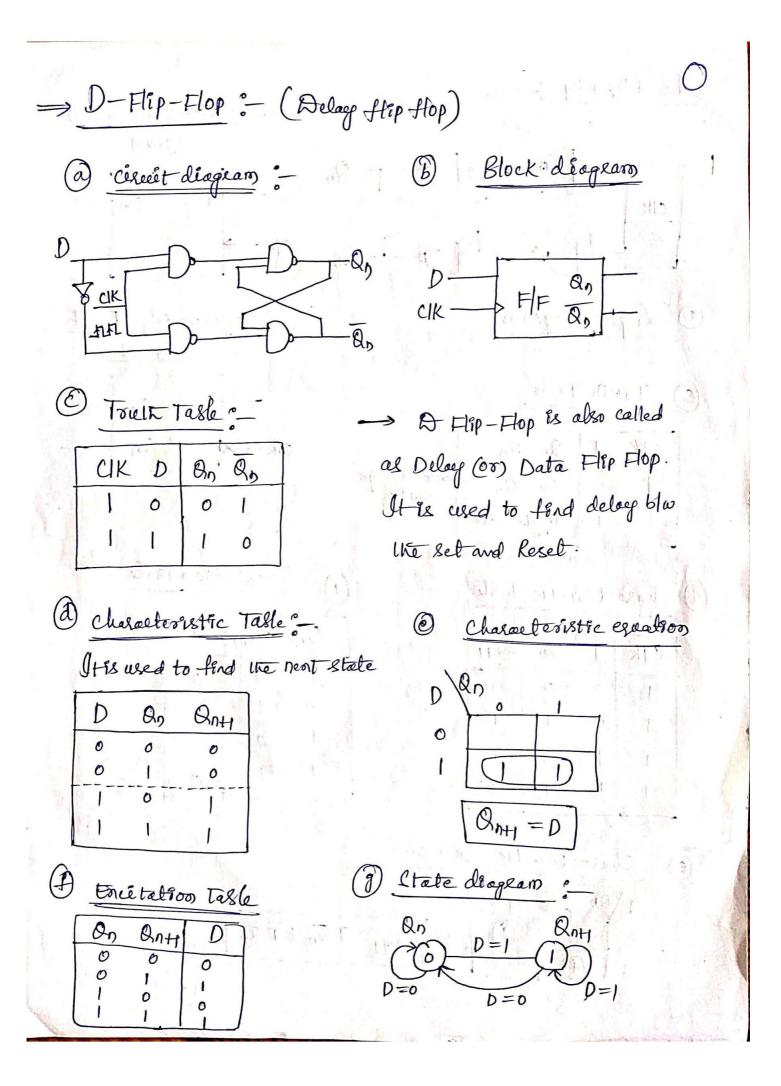

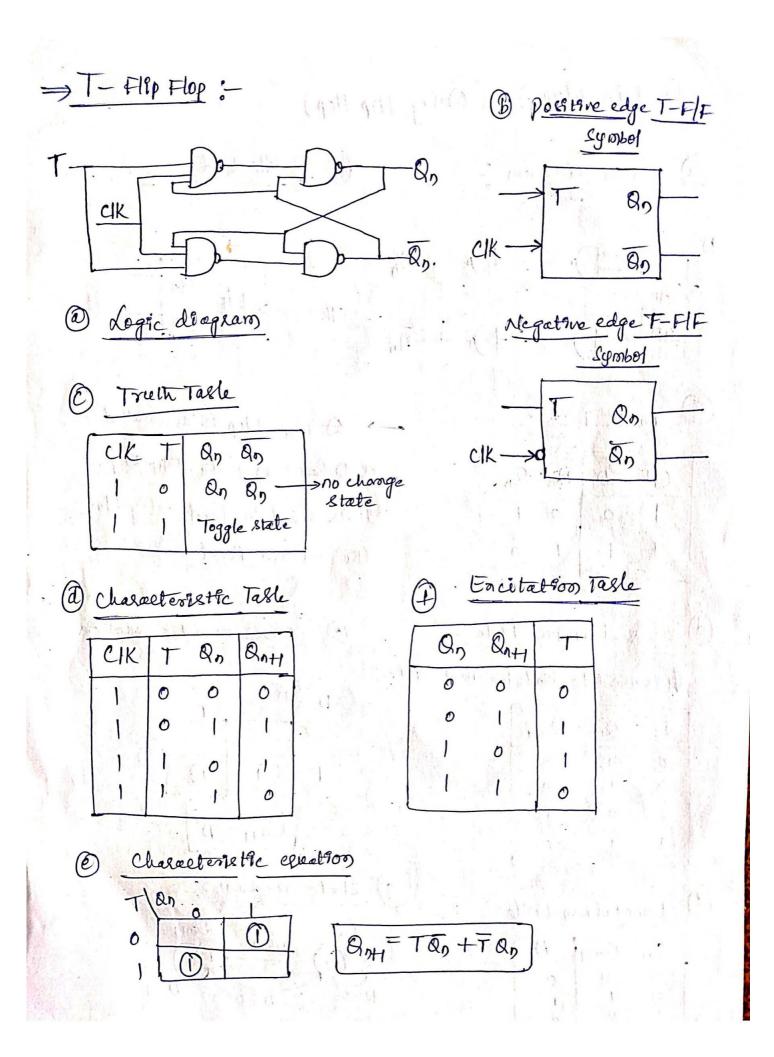

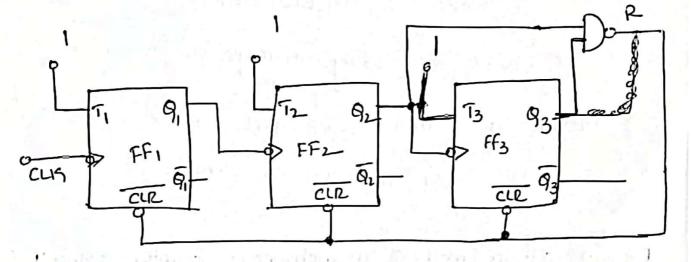

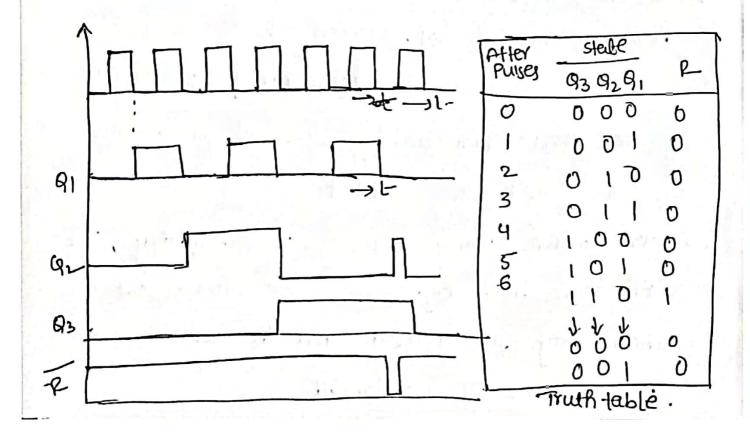

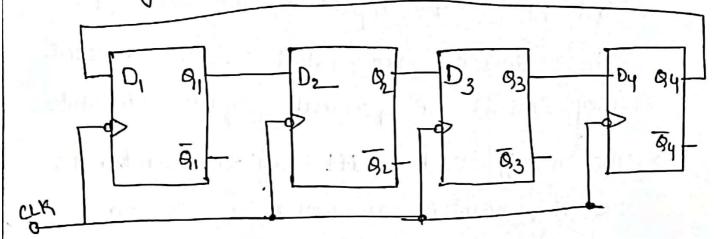

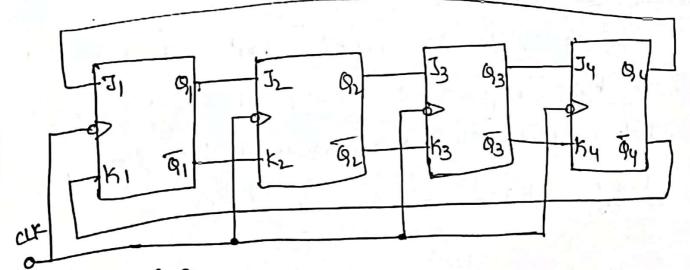

**UNIT II:** Digital logic circuits: Combinatorial Circuits: Introduction, Combinatorial Circuit Design Procedure, Implementation using universal gates, Multi-bit adder, Multiplexers, Demultiplexers, Decoders Sequential Switching Circuits: Latches and Flip-Flops, Ripple counters using T flip-flops; Synchronous counters: Shift Registers; Ring counters

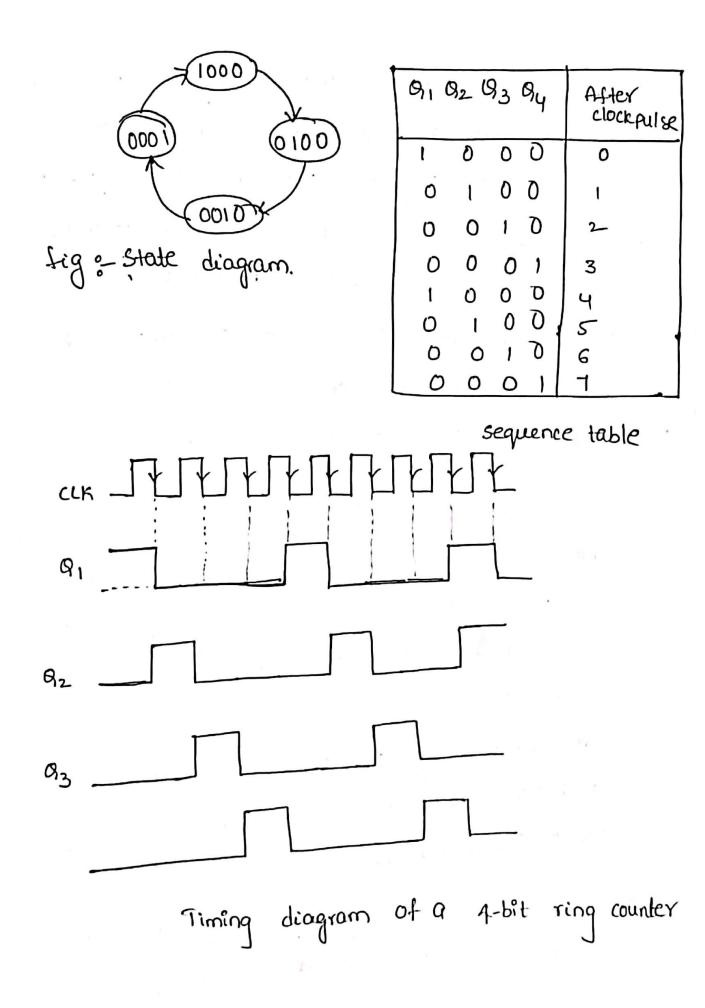

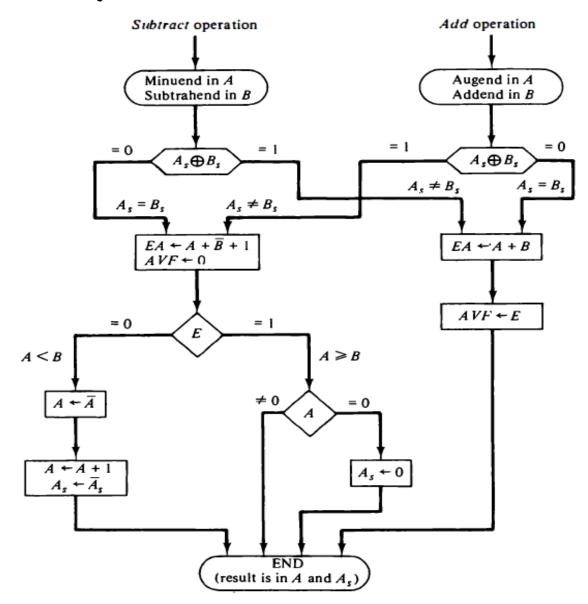

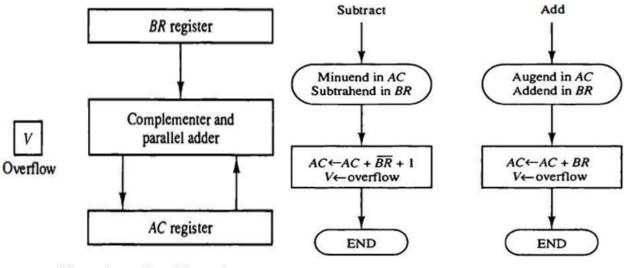

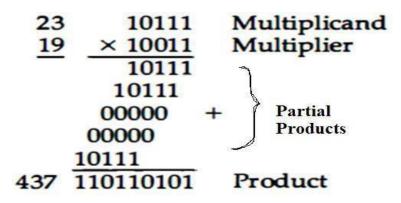

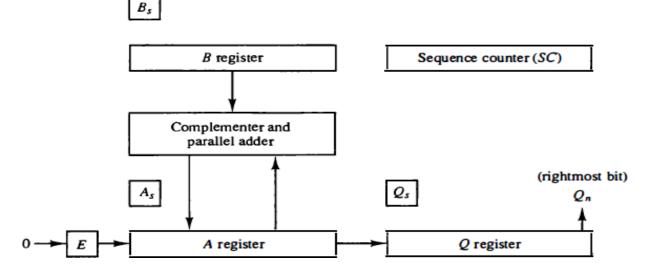

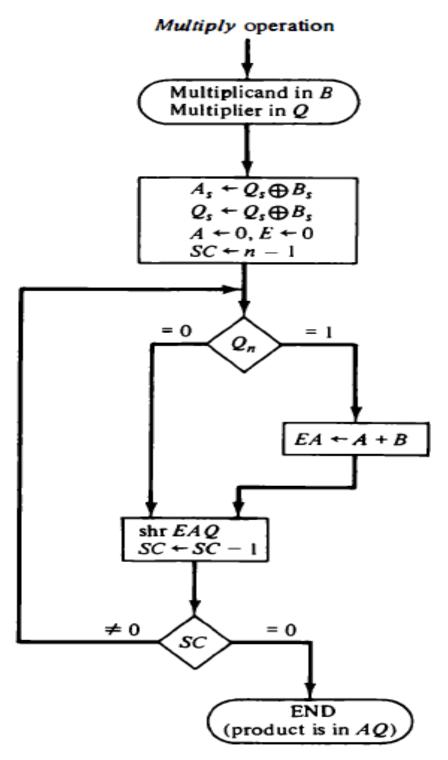

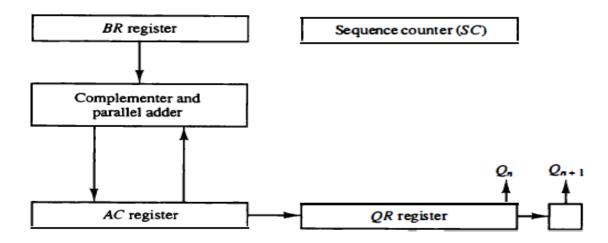

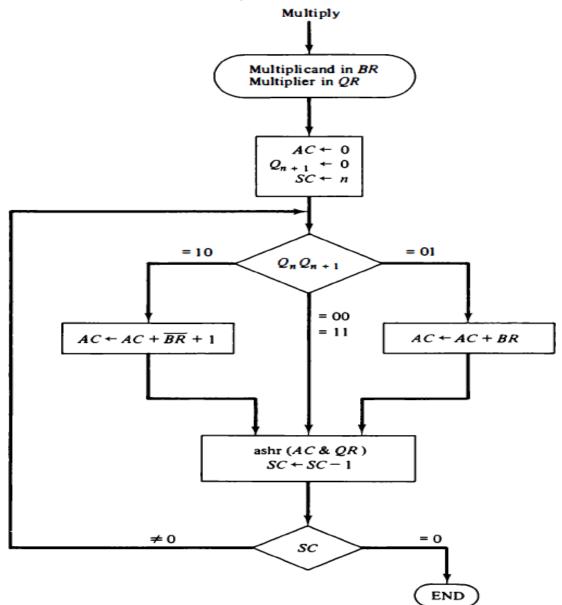

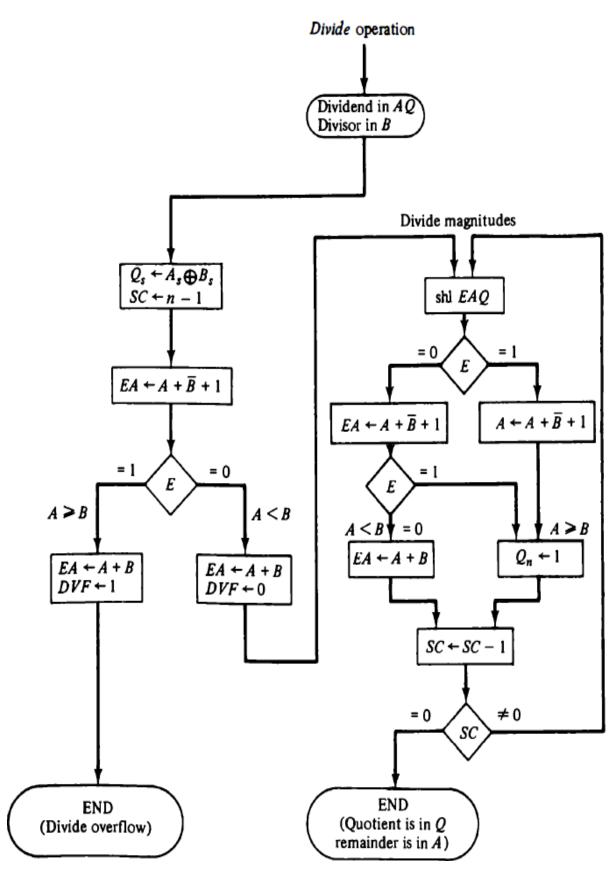

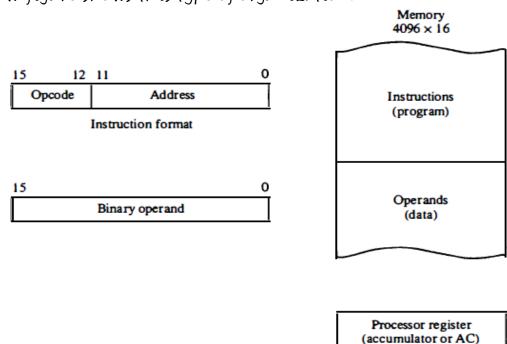

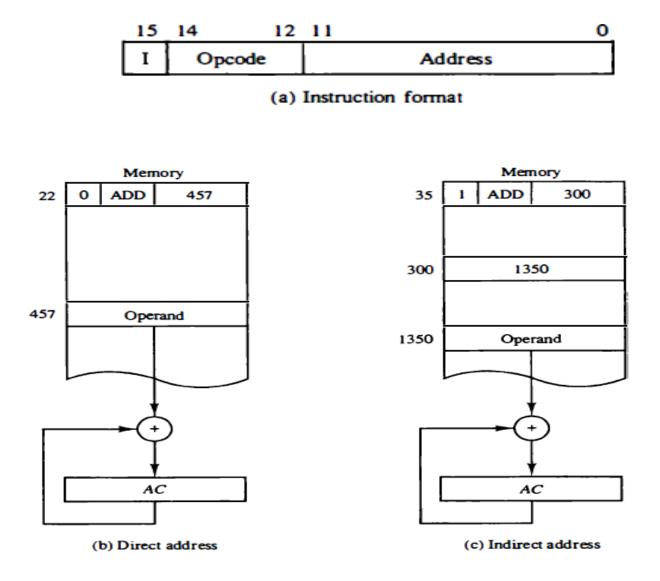

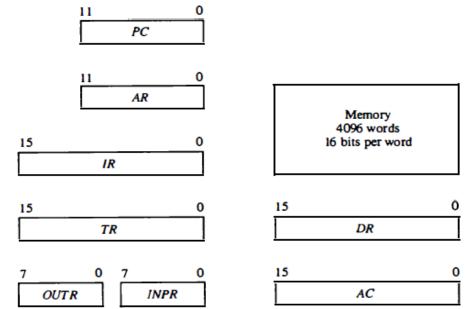

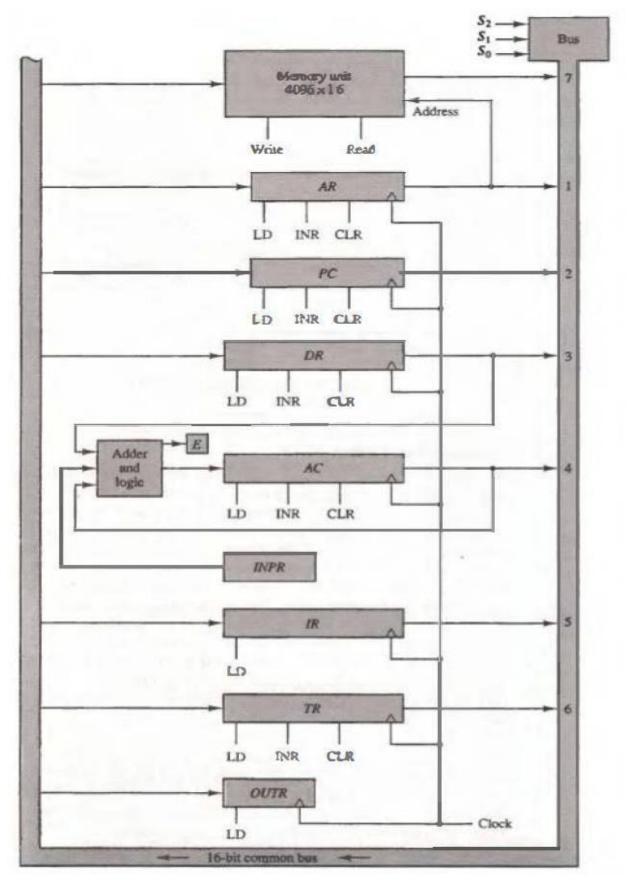

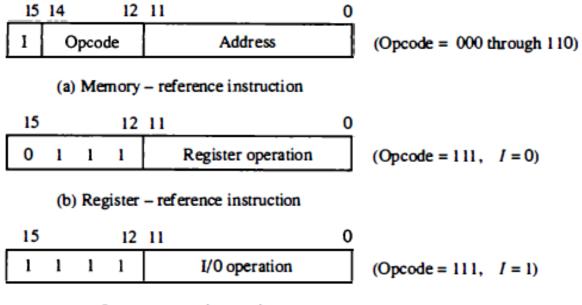

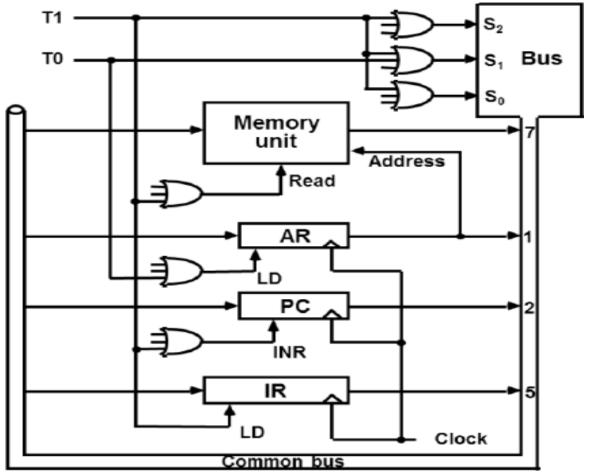

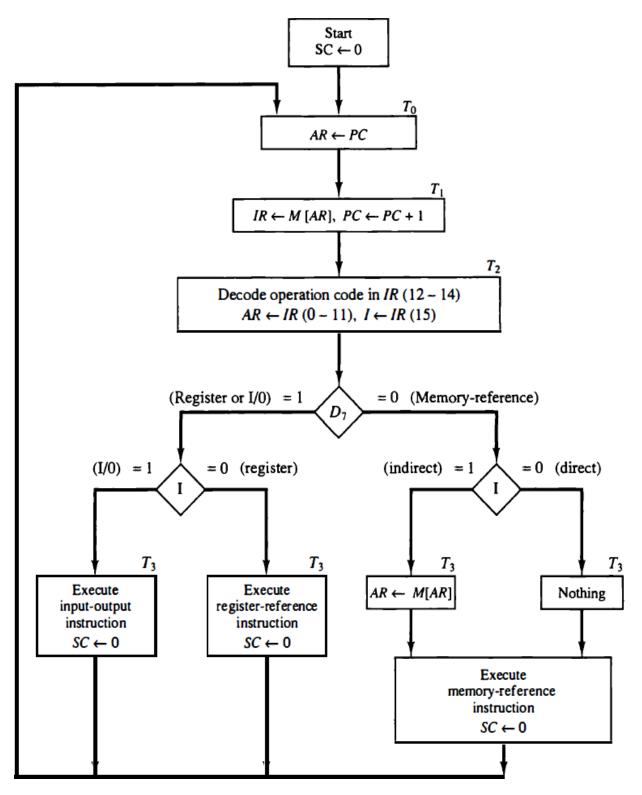

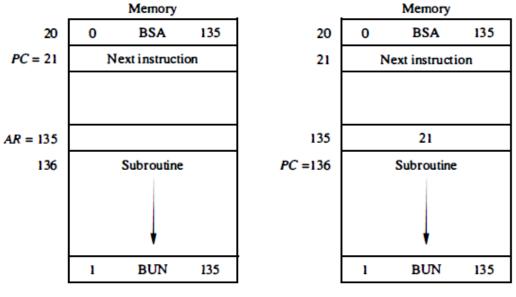

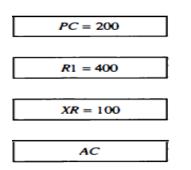

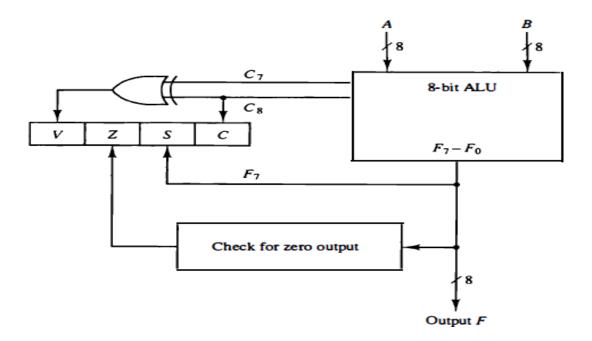

**UNIT III:** Computer Arithmetic: Addition and subtraction, multiplication Algorithms, Booth multiplication algorithm, Division Algorithms, Floating – point Arithmetic operations. Register Transfer language and microinstructions :Bus memory transfer, arithmetic and logical micro-operations, shift and rotate micro-operations Basic Computer Organization and Design: Stored program concept, computer Registers, common bus system, Computer instructions, Timing and Control, Instruction cycle, Memory Reference Instructions, Input–Output configuration and program Interrupt.

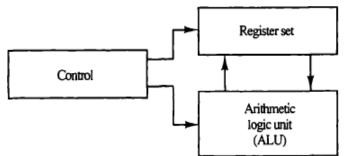

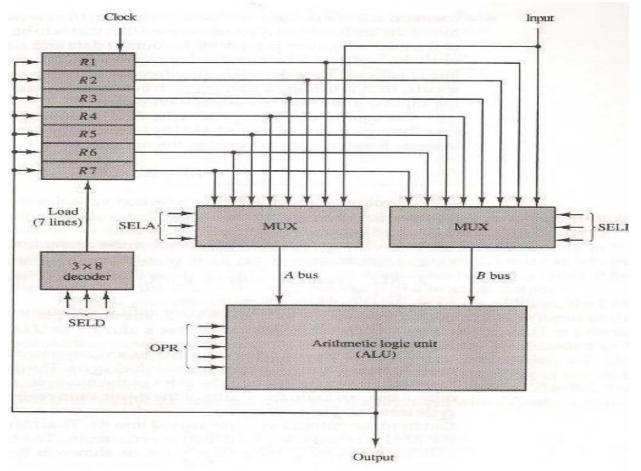

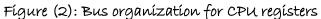

**UNIT IV:** Microprogrammed Control: Control memory, Address sequencing, microprogram example, design of control unit. Central Processing Unit: General Register Organization, Instruction Formats, Addressing modes, Data Transfer and Manipulation, Program Control: conditional Flags and Branching

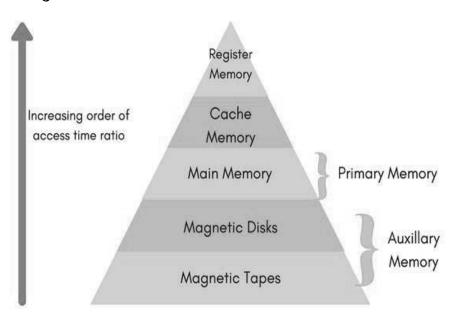

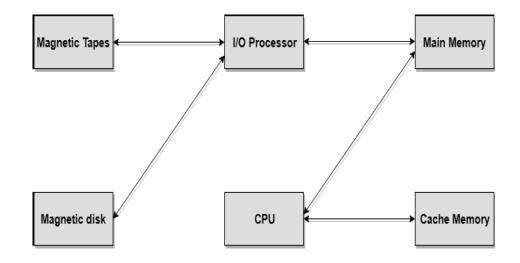

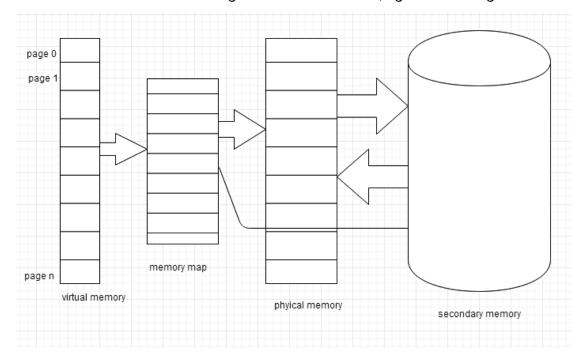

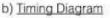

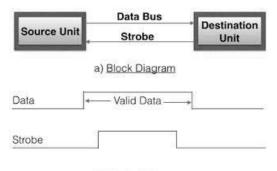

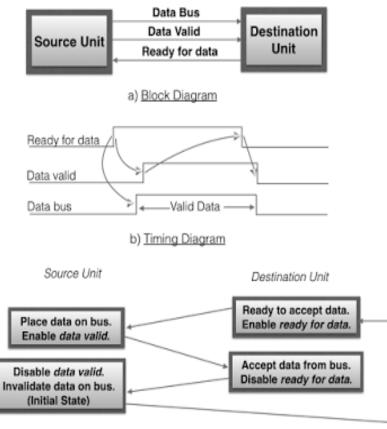

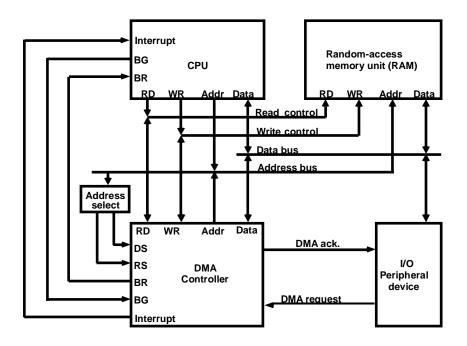

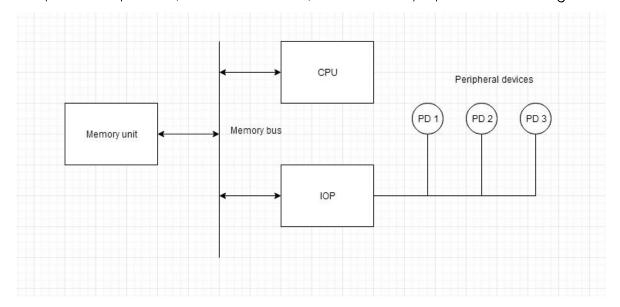

**UNIT V:** Memory Organization: Memory Hierarchy, Main Memory, Auxiliary memory, Associate Memory, Cache Memory. Input-Output Organization: Input-Output Interface, Asynchronous data transfer, Modes of Transfer, Priority Interrupt Direct memory Access.

**Text Books:** 1. Digital Logic and Computer Design,Moriss Mano,11thEdition,PearsonEducation. 2. Computer System Architecture,3rded., M.MorrisMano, PHI

Reference Books: 1. Digital Logic and Computer Organization, Rajaraman,Radhakrishnan,PHI,2006 2. Computer Organization, 5thed.,Hamacher, VranesicandZaky,TMH,2002 3. Computer Organization & Architecture :Designing for Performance, 7thed., William Stallings, PHI, 2006 Course Outcomes: By the end of the course the student will be able to

- > Demonstrate and understanding of the design of the functional units of a digital computer system.

- > Relate Postulates of Boolean algebra and minimize combinational functions.

- > Recognize and manipulate representations of numbers stored in digital computers.

- > Build the logic families and realization of logic gates.

- > Design and analyze combinational and sequential circuits.

- Recall the internal organization of computers, CPU, memory unit and Input/Outputs and the relations between its main components.

- Solve elementary problems by assembly language programming.

## VSM COLLEGE OF ENGINEERING RAMACHANDRAPURAM DEPARTMENT OF HUMANITIES AND BASIC SCIENCES

| Course Title | Year/Sem | Branch | Periods per Week |

|--------------|----------|--------|------------------|

| COMPUTER     | I / II   | CSE    | 6                |

| ORGANIZATION |          | BRANCH |                  |

#### **Course Outcomes:**

By the end of the course the student will be able to

- Demonstrate and understanding of the design of the functional units of a digital computer system.

- > Relate Postulates of Boolean algebra and minimize combinational functions.

- Recognize and manipulate representations of numbers stored in digital computers.

- > Build the logic families and realization of logic gates.

- > Design and analyze combinational and sequential circuits.

- Recall the internal organization of computers, CPU, memory unit and Input/Outputs and the relations between its main components.

- Solve elementary problems by assembly language programming.

| Unit<br>No | Outcomes                                                                                                                                                                                                                                                                                                                                            | Name of the Topic                                                                                                                   | No. of<br>Periods<br>required | Total<br>Periods | Reference<br>Book | Methodology<br>to be adopted |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|------------------|-------------------|------------------------------|

|            |                                                                                                                                                                                                                                                                                                                                                     | Unit-1 Digital Computers and Data<br>Representation                                                                                 |                               |                  |                   |                              |

|            |                                                                                                                                                                                                                                                                                                                                                     | Introduction ,Numbering Systems                                                                                                     | 1                             |                  |                   | Black Board                  |

|            |                                                                                                                                                                                                                                                                                                                                                     | Decimal to Binary Conversion, Binary<br>Coded Decimal Numbers, Weighted<br>Codes, Self Complementing Codes,                         | 2                             |                  |                   | Black Board                  |

|            |                                                                                                                                                                                                                                                                                                                                                     | Cyclic Codes, Error Detecting Codes,<br>Error Correcting Codes,                                                                     | 2                             |                  |                   | E-Class Room                 |

|            | I       Demonstrate       A         and       I       I         understanding       O         of the design of       I         the functional       I         units of a       I         digital       I         computer       I         system.       I         I       I         I       I         I       I         I       I         I       I | Hamming Code for Error Correction,<br>Alphanumeric Codes, ASCI Code, Data<br>Representation: Data types,<br>Complements,            | 2                             |                  |                   | E-Class Room                 |

| Ι          |                                                                                                                                                                                                                                                                                                                                                     | Fixed Point Representation, Floating Point Representation.                                                                          | 1                             | 14               | T1, T2<br>R20     | E-Class Room                 |

|            |                                                                                                                                                                                                                                                                                                                                                     | <b>Boolean Algebra</b> :Theorems and properties, Boolean functions, canonical and standard forms                                    | 1                             |                  |                   | Seminar                      |

|            |                                                                                                                                                                                                                                                                                                                                                     | minimization of Boolean functions using algebraic identities;                                                                       | 1                             |                  |                   | Black Board                  |

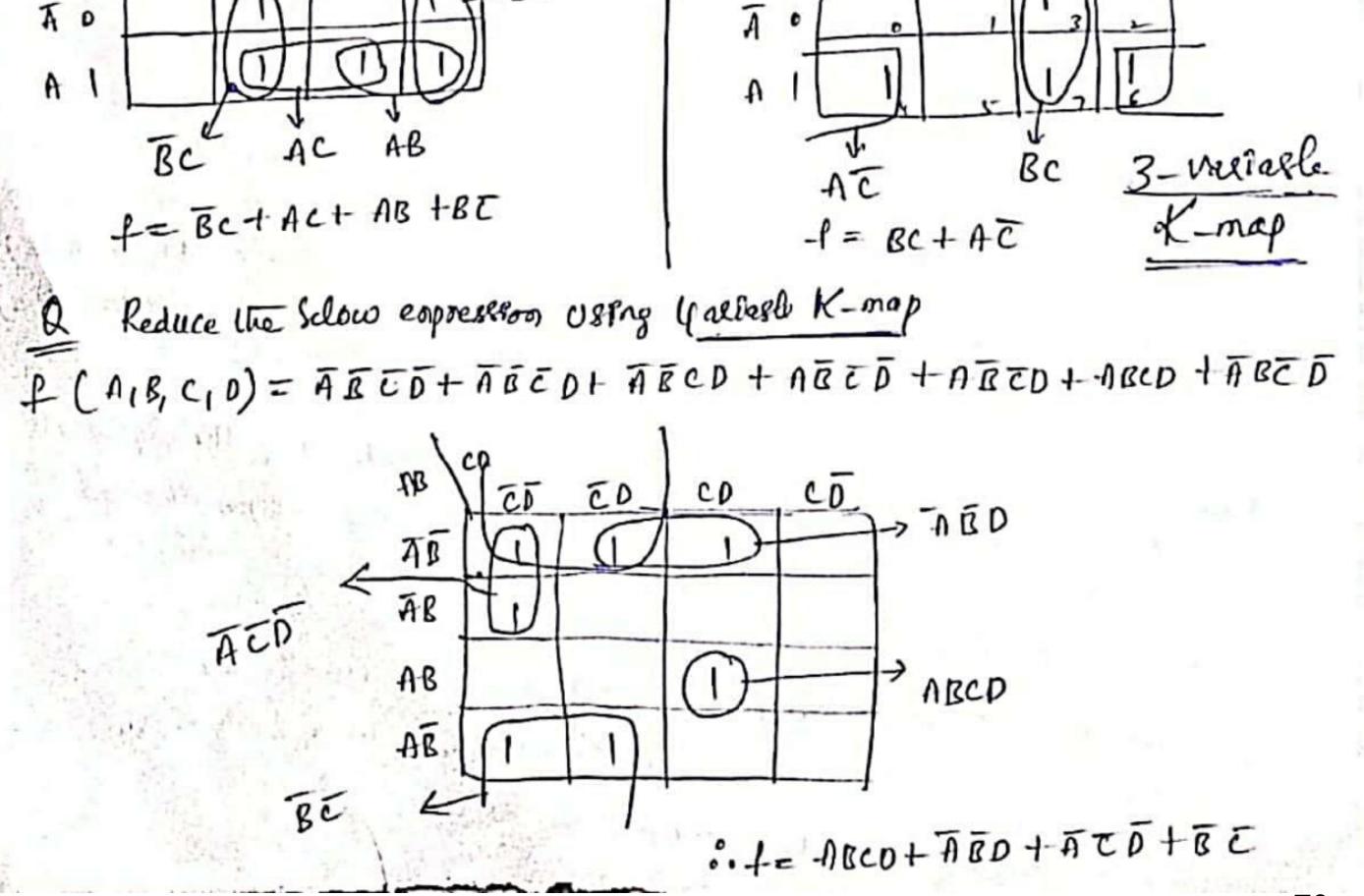

|            |                                                                                                                                                                                                                                                                                                                                                     | Karnaugh map representation and<br>minimization using two and three<br>variable Maps                                                | 2                             |                  |                   | Black Board                  |

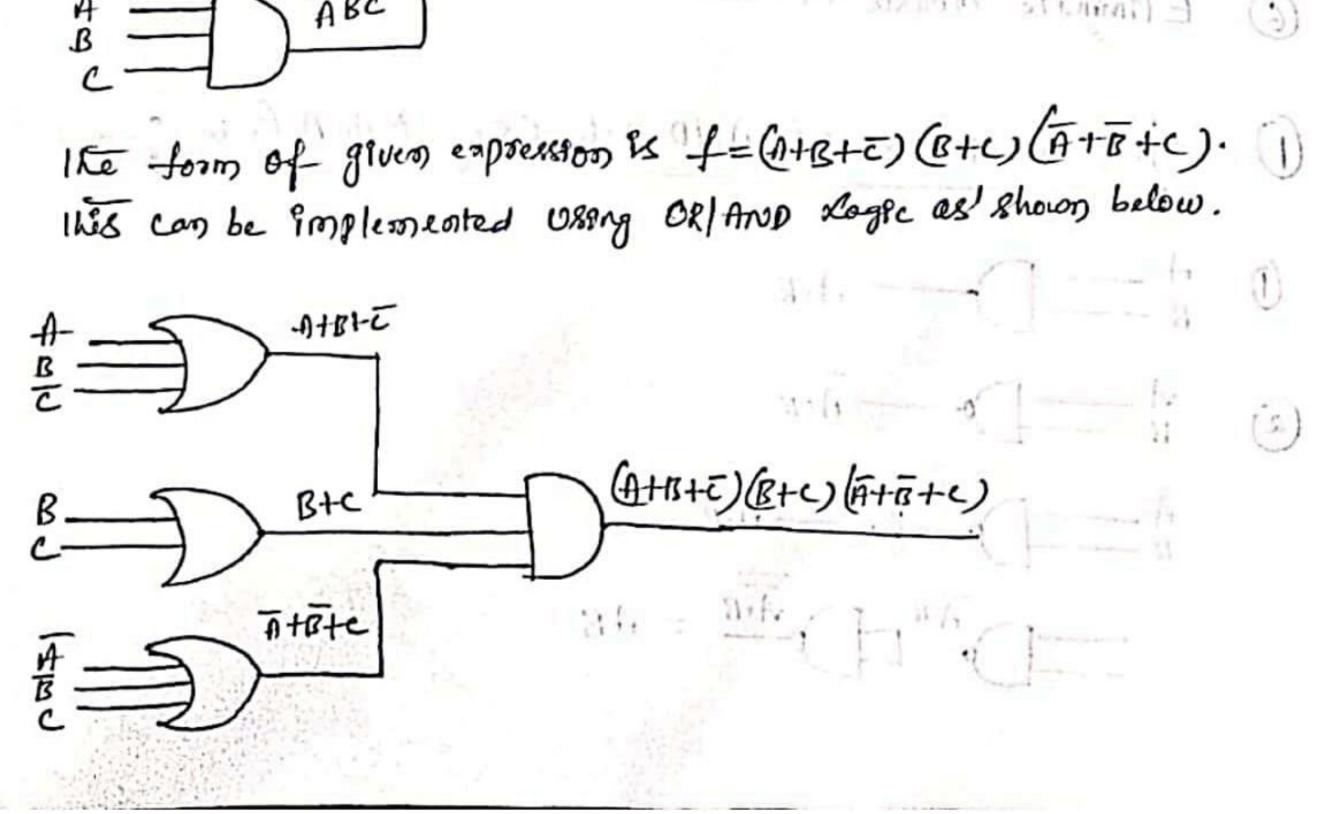

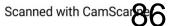

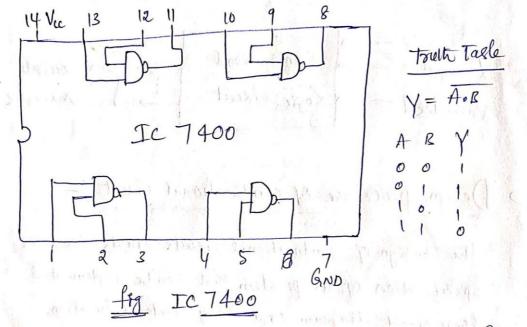

|            |                                                                                                                                                                                                                                                                                                                                                     | Logical gates ,universal gates and Two-<br>level realizations using gates : AND-<br>OR, OR-AND, NAND-NAND and<br>NOR-NOR structures | 2                             |                  |                   | E-Class Room                 |

|                         |                                        | Unit-2 Digital logic circuits,<br>Sequential Switching Circuits                                                        |   |   |               |              |

|-------------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------|---|---|---------------|--------------|

|                         | <u>CO 2</u> :                          | Combinatorial Circuits: Introduction,<br>Combinatorial Circuit Design<br>Procedure                                     | 1 |   |               | Black Board  |

| Relate<br>Postulates of | Relate<br>Postulates of                | late Implementation using universal gates,                                                                             |   |   |               | E-Class Room |

| II                      | Boolean algebra and                    | Multiplexers, Demultiplexers,<br>Decoders                                                                              | 2 | 9 | T1, T2<br>R20 | E-Class Room |

| cor                     | minimize<br>combinational<br>functions | Latches and Flip-Flops, Ripple<br>counters using T flip-flops                                                          | 2 |   |               | Black Board  |

|                         |                                        | Synchronous counters: Shift Registers;<br>Ring counters                                                                | 2 |   |               | E-Class Room |

|                         |                                        | Unit-3 Computer Arithmetic,<br>Register Transfer language and<br>microinstructions, Basic<br>Computer Organization and |   |   |               |              |

|     |                                                                                                          | Computer Organization and<br>Design                           |            |     |              |              |

|-----|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|------------|-----|--------------|--------------|

|     |                                                                                                          | Addition and subtraction,<br>multiplication Algorithms        | 2          |     |              | Black Board  |

|     |                                                                                                          | Booth multiplication algorithm,<br>Division Algorithms        | 2          |     |              | E-Class Room |

|     |                                                                                                          | Floating – point Arithmetic operations                        | 2          |     |              | Black Board  |

|     | CO 3 :<br>Recognize and<br>manipulate<br>representations<br>of numbers<br>stored in digital<br>computers | Bus memory transfer, arithmetic and logical micro-operations  | 2          |     |              | Black Board  |

|     |                                                                                                          | shift and rotate micro-operations                             | 1          | 1.7 | T1, T2       | Black Board  |

| 111 |                                                                                                          | Stored program concept, computer Registers, common bus system | - <u> </u> | R20 | E-Class Room |              |

|     |                                                                                                          | Computer instructions, Timing and<br>Control                  | 2          |     |              | Black Board  |

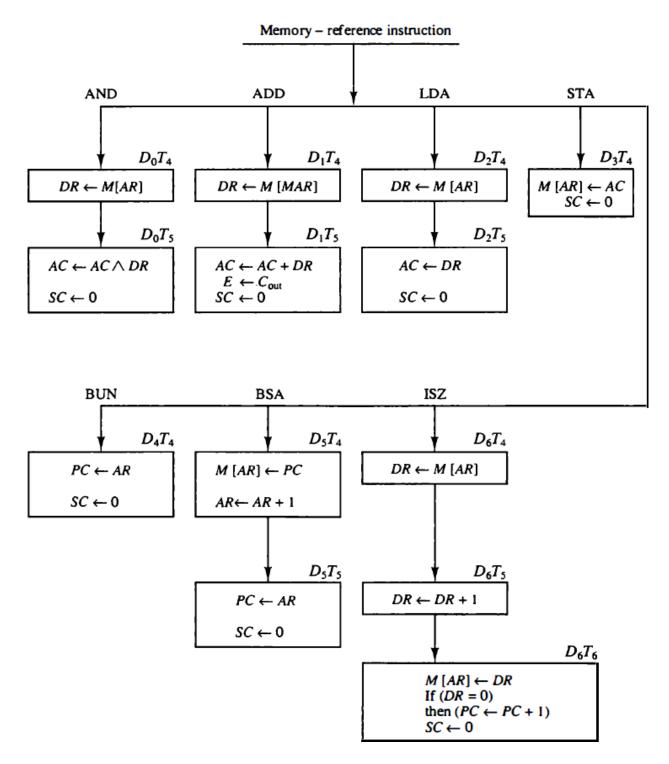

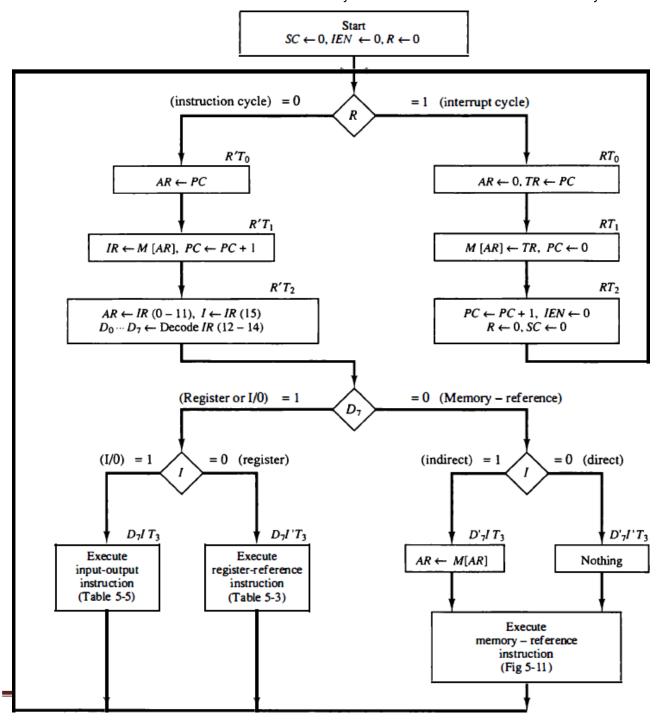

|     |                                                                                                          | Instruction cycle, Memory Reference<br>Instructions           | 2          |     | Black Board  |              |

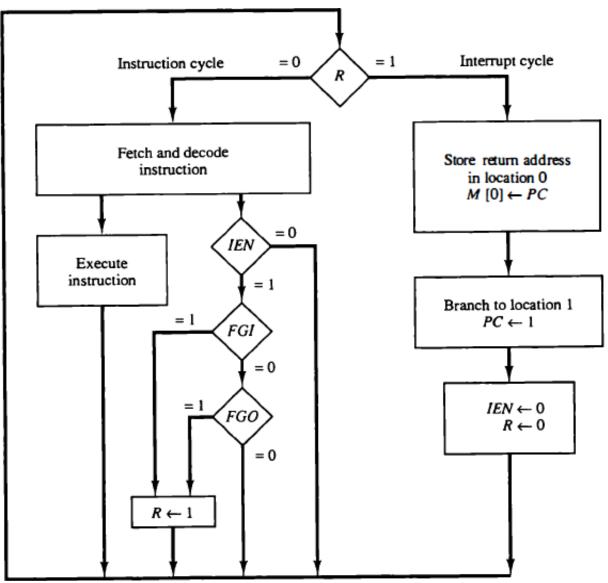

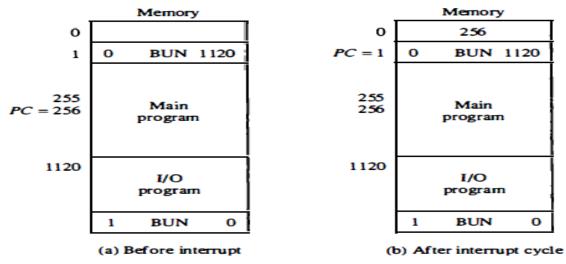

|     |                                                                                                          | Input–Output configuration and<br>program Interrupt           | 2          |     |              | E-Class Room |

|    |                                                                  | Unit-4 Micro programmed<br>Control , Central Processing Unit  |   |      |               |              |

|----|------------------------------------------------------------------|---------------------------------------------------------------|---|------|---------------|--------------|

|    | <u>CO4</u> :                                                     | Control memory, Address sequencing                            | 2 |      |               | Black Board  |

|    | Build the<br>logic families                                      | Micro program example, design of control unit                 | 2 | 4    |               | Black Board  |

| IV | and<br>realization of<br>logic gates,                            | General Register Organization,<br>Instruction Formats         | 2 | - 10 | T1, T2        | E-Class Room |

|    | Design and<br>analyze<br>combinational                           | Addressing modes, Data Transfer and Manipulation              | 2 |      | R20           | E-Class Room |

|    | and sequential circuits.                                         | Program Control: conditional Flags and<br>Branching           | 2 |      |               | Black Board  |

|    |                                                                  | Unit-4 Memory Organization ,<br>Input-Output Organization     |   |      |               |              |

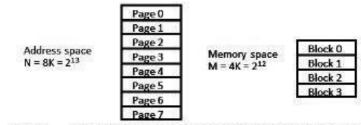

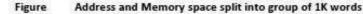

|    | CO5:<br>Recall the                                               | Memory Hierarchy                                              | 2 |      |               | Black Board  |

|    | internal<br>organization<br>of computers,<br>CPU,                | Main Memory , Auxiliary memory                                | 2 |      |               | E-Class Room |

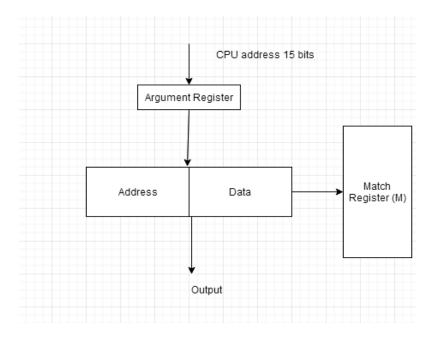

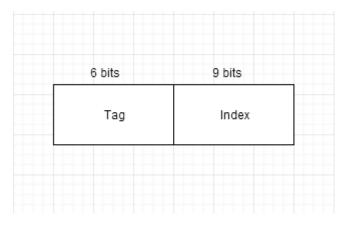

| v  | memory unit<br>and<br>Input/Outputs<br>and the<br>relations      | Associate Memory , Cache Memory                               | 2 | 10   | T1, T2<br>R20 | Black Board  |

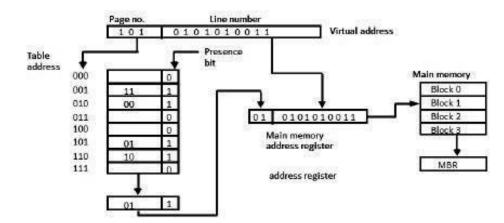

|    | between its<br>main<br>components ,<br>Solve                     | Input-Output Interface, Asynchronous<br>data transfer         | 2 |      |               | E-Class Room |

|    | elementary<br>problems by<br>assembly<br>language<br>programming | Modes of Transfer, Priority Interrupt<br>Direct memory Access | 2 |      |               | Black Board  |

|  | TOTAL | 60 |  |

|--|-------|----|--|

|  |       |    |  |

**Text Books:** 1. Digital Logic and Computer Design, Moriss Mano, 11thEdition, PearsonEducation. 2. Computer System Architecture, 3rded., M.MorrisMano, PHI

Reference Books: 1. Digital Logic and Computer Organization, Rajaraman, Radhakrishnan,PHI,2006 2. Computer Organization, 5thed.,Hamacher, VranesicandZaky,TMH,2002 3. Computer Organization & Architecture : Designing for Performance, 7thed., William Stallings, PHI, 2006

**Faculty Member**

Head of the Department

Principal

# **UNIT - 1**

Starrage in the second se

Introduction :- <u>Computer</u> is a machine that can stoke and peocess information. Most computers kely on a binary system that uses two variables 0 and 1 to complete tasks system that uses two variables 0 and 1 to complete tasks such as storing data calculating algorithms and displaying information. <u>Organization</u> :- Group of people who work together and to reach a goal by using peoper system. <u>System</u> :- A set of things working together to accomplish particular Goal. <u>Ea</u>:- School system, college system and Raelway system. <u>Number system</u> :- Represent data in digital form.

Contract of

Binder Number System: - A Number is made up of a collection of digits and it has two parts. (a) Genteger part (b) Exaction part Bolt are separated by a radia point (c). The number is represented as d, d, ---- d, do j, d, d, --- d Integer part Radia Fractional Point Part. Number systems are classified as Binary Number system

- (6) Decemel Number System

- (C) Octal Number system

a

(6)

いいのないで

(a) Hena decemal Nuesober system.

the Binary number system is a Redia-2. This is represented internal of 0 and 1. The Redia point is Known as the binary point and 0 and 1 is a binary bits.

The decimal number system is a radia -10. These are 0, 1, 2, 3, 4, 5, 6, 7, 8 and 9 (0-9). The radia point is Known as decimal point.

Octal number system is a radia 8. They are 0, 1, 7, 3, 4, 5, 6, and 7 (0-7). The radia point is known as actal Doint.

Decimal number system to Binazep number system conversion.

$$\begin{array}{c}

(25)_{10} = (?)_{2} \\

(25)_{10} = (?)_{2} \\

(25)_{10} = (?)_{2} \\

(25)_{10} = (?)_{2} \\

(25)_{10} = (?)_{2} \\

(25)_{10} = (?)_{2} \\

(25)_{10} = (?)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\

(25)_{10} = (1001)_{2} \\$$

1 1 1 1 1 A

200 - 12 - 1 - 1

$= \frac{\text{Feartfonal part }'_{-}}{3} \underbrace{(0.25)}_{10} = \underbrace{(2)}_{2} \\ \text{Top to}_{2} \\ \text{Bottom}_{3} \\ 0.35 \\ \times 2 = 0.5 \\ 0.5 \\ \times 2 = 1.0 \\ 0.0 \\ \times 2 = 0.0 \\ 0 \end{bmatrix}$

14238 m 5-

4 × 14 10 500

the second

0.0 X2 = 0 -> ignore it Whenevers we get repeated Numbers just ignore it

$(.(0.25) = (0.010)_{2}$

(1)

$$(0.8125) = (?)$$

1 148- WTT

- $0.8125 \times 2 = 1.6250 \rightarrow 1$   $0.6250 \times 2 = 1.250 \rightarrow 1$  $0.250 \times 2 = 0.50 \rightarrow 0$

- 0.50 X 2 = 1.0 -> 1

- 0.0 x 2 = 0.0 ->0 1

Topto Rottom

: (0.8125) = (0.11010)

(10.625) = (?)5

$$2 10$$

$2 5-0 1$

$2 2-1$

$1-0$

(1010)

$$\begin{array}{c} 0.625 \times 2 = 1.250 \longrightarrow 1 \\ 0.250 \times 2 = 0.50 \longrightarrow 0 \\ 0.50 \times 2 = 1.0 \longrightarrow 1 \\ 0.0 \times 2 = 0.0 \longrightarrow 0 \\ \end{array}$$

$$\begin{array}{c} (10.625) = (1010.1010) \\ 10 \end{array}$$

$$\widehat{(25.125)} = \binom{2}{2} \\ 2 (25.125) = \binom{2}{2} \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25) \\ 2 (25)$$

$$\begin{array}{c} 0 \cdot 125 \times 2 = 0 \cdot 250 \longrightarrow 0 \\ 0 \cdot 250 \times 2 = 0 \cdot 50 \longrightarrow 0 \\ 0 \cdot 5 \times 2 = 1 \cdot 0 \longrightarrow 1 \\ 0 \cdot 0 \times 2 = 0 \cdot 0 \longrightarrow 0 \end{array}$$

[:.(25.125) = (11001.0010)

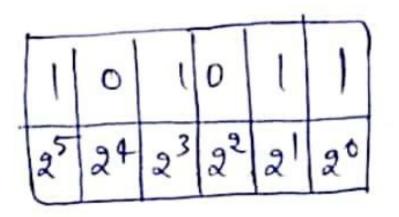

Renares Number system to Decemal number system conversion - $(1101)_{g} = C_{10}$ 0 ( Successive multiplication method) 0 23 22 21 20  $|x_2^3 + |x_2^2 + 0x_2^1 + |x_2^0 = 8 + 4 + 0 + 1 = 13 : (101) = (13)$ 2 10

Scanned with CamScanner

$$(101011)_{2} = (?)_{10}$$

$$[\chi_{2}^{5} + 0\chi_{2}^{4} + 1\chi_{2}^{3} + 0 + 2^{2} + 1\chi_{2}^{1} + 1\chi_{2}^{0} = 32 + 0 + 8 + 0 + 2 + 1$$

$$= 43$$

$$(101011) = (43)$$

$$\chi_{2} = 10$$

and a

「「「「「「「「「」」」」」」

50

-

$$(11010.010)_{2} = (?)_{10}$$

0 0 ٠ 2 22 20 22 21 -1, 1-3 0

- 3

$$\begin{aligned} |x_{a}^{2} + 0x_{a}^{2} + |x_{a}^{2} + 0x_{a}^{2}| + |x_{a}^{2} + 0x_{a}^{2} + 1x_{a}^{2} +$$

5

.....

10

1.00

たい、

1

۰.

Scanned with CamScanner

-

0001 01 BCD Decimal number 0001 0100 14 0010 0011 0100 234 0010 0011 1001. 0101 0110 239.56 0110 0101 0011. 1001 0116 653.96 \* Represent 356 in RCD format 3 5 6 ans -0101 0110. 1000 the grans

| 100         | 000) 0016 |

|-------------|-----------|

| only 4-19th | 8-6853.   |

Phin ?

Note: Feom the above concept, we can conclude one thing that BCD is SIMPle to represent clearmal Numbers built some dimes it takes more no. of bits. So, it occupies memory. Arsitemetric Operations are more complex than the Binaleg. Arsitemetric Operations are more complex than the Binaleg. 92 in Binary representation 92 in BCD V

64 32 16 8421 1001 0010

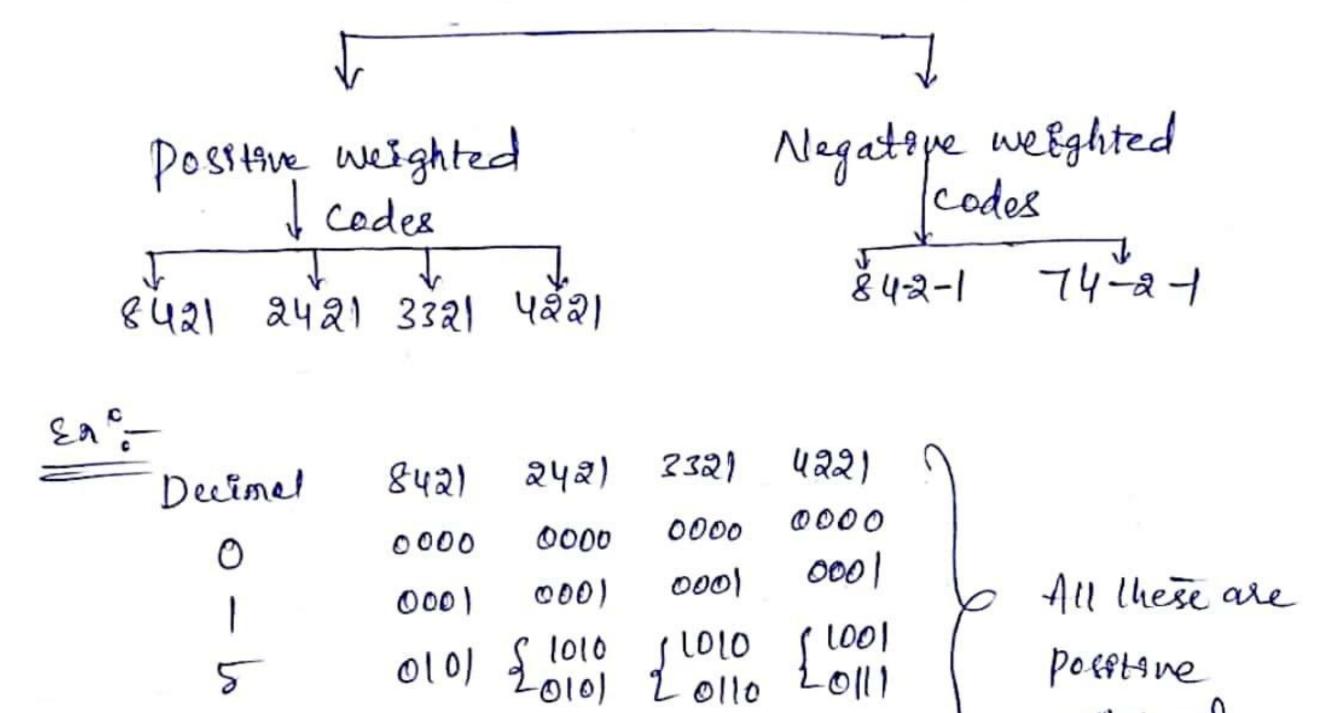

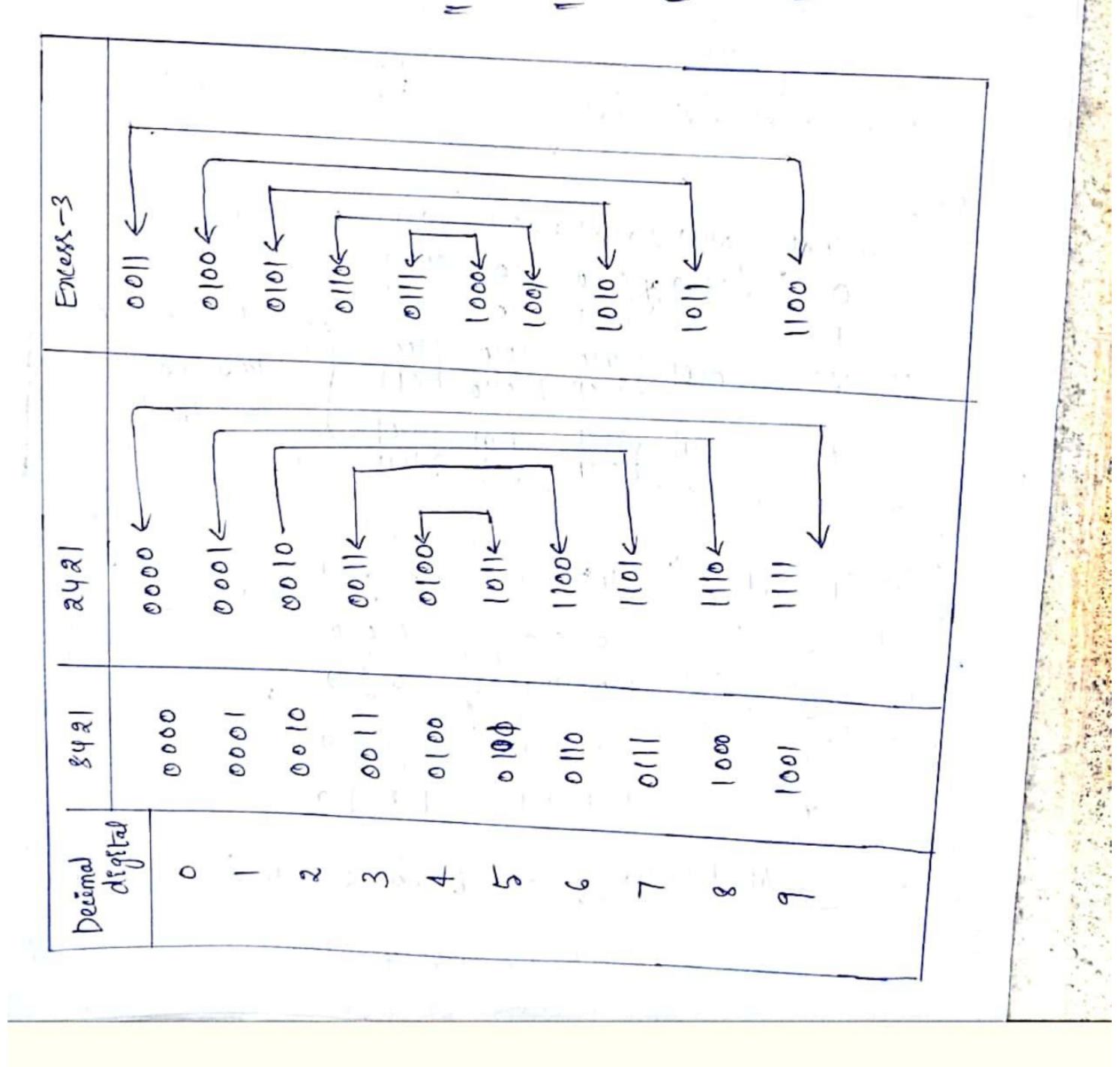

⇒ Weighted codes :- the weighted codes are those which Obey the position weighting peoncepte. Each position of the number represents a Specific weight.

weight code

1101 1101 0111 51101

Sa- permet 74-2-1 84-2-1 0000 0000 0 1010 011 5 000 00 9 0 11 > Non-weighted codes Enless-2 code. Gray code

⇒ Seff-complementing code :- It is said to be self-complementing if the code word of the 9's complement of N i. e. 9-N can be obtained from the code word of N by interchanging all the O's and 1's. En: 2421, 5211, 642-3, 84-2-1 & Eacers-3. 2tutati Statith Glut2-3 844-2-1 =9 =9 =9 =9 =9

ころうちのとう とうないかっていたいちょう ちょうちょう

The second se

14 .

2

1

-

1111

- Car

3 ۰,

Cyclic codes :- cyclic codes are litose in which each different from the preceding one in onleg 1-51 position. cyclic codes are also called as unit destance codes En: Gracy code.

Cracy code is also called as Reffective code.

Reflective code means in supplic code 0-7 is the missor interface of 8-15. Gracy code is not a sequence code. Inage of 8-15. Gracy code is not a sequence code. Inage of 8-15. Gracy code is not a sequence code. Inage of 8-15. Gracy code is not a sequence code. Inage of 8-15. Gracy code is not a sequence code. Inage of 8-15. Grace code is not a sequence code. Inage of 8-15. Grace code is not a sequence code. Inage of 8-15. Grace code is not a sequence code. Inage of 8-15. Grace code is not a sequence code. Inage of 8-15. Grace code is not a sequence code. Inage of 8-15. Grace code is not a sequence code. Code is not a sequence code. Inage of 8-15. Grace code is not a sequence code. Inage of 8-15. Grace code is not a sequence code. Inage of 8-15. Grace code is not a sequence code. Inage of 8-15. Grace code is not a sequence code. Code is not a sequence code. Inage of 8-15. Grace code is not a sequence code. Inage of 8-15. Grace code is not a sequence code. Inage of 8-15. Grace code is not a sequence code. Inage of 8-15. Grace code is not a sequence code. Inage of 8-15. Grace code is not a sequence code.

$\begin{array}{cccc} \underline{Decimal} & \underline{Binareg} & \underline{Graeg} \\ \underline{N0:} & 0000 \longrightarrow 0000 & \underline{Sof} & 1010 \\ 0 & 0000 \longrightarrow 0001 & \underline{Sof} & 1010 \\ 1 & 0001 \longrightarrow 0001 & \underline{Sof} & 1010 \\ \end{array}$

ans 1111 0010 ----> 0011-> Convert (0110) to gray 00 -----Code 0 0 1 000 ---ans 1001 -----X-OR Fruite Table 1010-ABB A B ь 1111-Ò

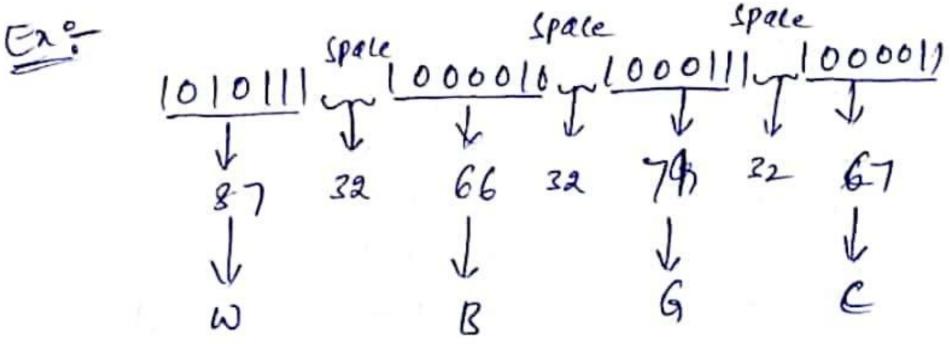

⇒ AlphaNumeric codes :- These are the codes which represent alphanameric information i.e letters of the alphabet and decimal numbers as a sequence gots and \$\$.

Eq:- ASCII, EBCDIC codes

→ ASCII → American Atandard code for information interchange

→ EBCDIC → Entended lineary coded decimal interchange code.

→ Alphanumeric codes consists of numbers as well as alphabetic characters.

→ Jt contains R6 Alphabets write Capital d Small letters, numbers (0-9), panctuation marks and other symbols.

→ ASCIE code is a 7-551-code and more commonly used woldwide.

→ ASCIE code is a 7-551-code and more commonly used woldwide.

| -> | EBCORC code                                                                                                                                                                                         | 1. $a^{1} = 128$ symbols<br>18 $a^{8} = 256$ symbols                                                                                                                                                             | used 95 large <u>ERM</u> computers.<br>The used International<br>Basenese<br>machine.                                                                                                                                           |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | $32 \rightarrow \text{space}$ $33 \rightarrow !$ $34 \rightarrow ?$ $35 \rightarrow ?$ $36 \rightarrow $$ $37 \rightarrow ?$ $28 \rightarrow ?$ $39 \rightarrow \text{C}$ $40 \rightarrow \text{T}$ | $42 \rightarrow *$ $43 \rightarrow +$ $44 \rightarrow ,$ $45 \rightarrow -$ $46 \rightarrow .$ $47 \rightarrow /$ $48 \rightarrow 57 \rightarrow (0-9)$ $58 \rightarrow :$ $59 \rightarrow ;$ $60 \rightarrow <$ | $61 \rightarrow =$ $62 \rightarrow 7$ $63 \rightarrow ?$ $64 \rightarrow @$ $65 - 90 (A - z) capital letters$ $91 \rightarrow \Box$ $92 \rightarrow 1$ $93 \rightarrow \Box$ $94 \rightarrow 1$ $95 \rightarrow - (undersecre)$ |

arte

-> ASCII codes are used in miceo computer (r) personal computer

14

Error CORRecting Codes - Codex which allow Error detection and correction are called Error correcting code.

Eg :- Hamming code.

Hamming code is a specific type of error correcting code that allows the detection and consection of single soft transmission errors. Hamming code algorithm can rolve only single tote issues. These are used in setellite communication.

Ea: Encode the data on message sits 0011 into the 7-litereven parity Hamming code.

Set Given message solar Market is calculated using the formula Number of parity Sitz représed is calculated using the formula perimal 2<sup>2</sup> 2<sup>1</sup> 2<sup>0</sup>

$P_2 = 2, 3, 6, 7 = P_2 | 00$  = 1|00  $P_2 = 0$   $P_2 = 0$   $P_3 = 4, 5, 6, 7 = P_3 | 00$  to become the even perity (: P\_3 = 1) = 1|00

$P_{3} = 1$

Sa:

Error possition = By combining the parity site  $f_2P_2P_1 = P_{\overline{1}}P_{\overline{2}}P_{\overline{3}} = ollo=(b)_{10}$ Error & located at 2rd possition Total message site = ooi 1 1 110 After consecting = 0111110.

Generate hamming code tor me message 1100

p= paloty St 2Z Ptm+1 m= message GTS So 2P= P+4+1 pshould be atleast 3 to satisfy the condition 2PZP+5 23 2 3+5 %. 828 (true) (The code may be any Longho the process 3 4 will be same) P3 m2 m2 m4 M P2 For even party) P3 P2 P1 P1 => 1,3,5,7 -> P,110 -> 0110 (P1=0) Pa ???,6,7 > P2/10 > 0110 (P2=0) P2 -> 45,6,7 -> P2110 ->0110 (P2=0)

Total message sftz

= 0 0 10 11 0

odd pasity "-

$$P_1 \Rightarrow 1_1 s_1 s_7 7 \rightarrow P_1 110 \rightarrow 1110 (P_1 = 1)$$

$P_2 \Rightarrow 2_1 s_1 6_1 7 \rightarrow P_2 110 \rightarrow 1110 (P_2 = 1)$

$P_3 \Rightarrow 4_1 s_1 6_1 7 \rightarrow P_2 110 \rightarrow 1110 (P_3 = 1)$

Total message sftz

= P\_1 P\_2 m\_1 P\_3 m\_2 m\_3 my

= 1 1 1 1 1 1 0

$\Rightarrow$  Error corrections for thermity code

$O_2 A (T_1 4)$  hamming code is secseved as 1110000 determine the

corrected code when even and odd pastity.

Sel  $i = 2 - 3 + 5 - 6 - 7$

$i = 1 + 0 = 0 = 0$

To ensure that error & there are not  $E_{1} \rightarrow 1, 3, 5, 7 \rightarrow 1100 \rightarrow to melle. It even part of$  $E_{1} = 0.$ (even) $Partity) = 2, 5, 6, 7 \rightarrow 1100 \Rightarrow E_{2} = 0$  $E_{2} \rightarrow 4, 5, 6, 7 \rightarrow 0000 \Rightarrow E_{2} = 0$  $Error = E_{2} E_{2} E_{1} = 000 (Ott possisson)$ Odd partity $E_{1} \rightarrow 1, 3, 5, 7 \rightarrow 1100 \rightarrow E_{1} = 1. (to make it - odd partion)$  $E_{2} \rightarrow 2, 3, 6, 7 \rightarrow 1100 \rightarrow E_{2} = 1 (to make it - odd partion)$  $E_{2} \rightarrow 2, 3, 6, 7 \rightarrow 1100 \rightarrow E_{2} = 1 (to make it - odd partion)$  $E_{2} \rightarrow 2, 3, 6, 7 \rightarrow 1100 \rightarrow E_{2} = 1 (to make it - odd partion)$  $E_{2} \rightarrow 2, 3, 6, 7 \rightarrow 1100 \rightarrow E_{2} = 1 (to make it - odd partion)$  $E_{2} \rightarrow 2, 3, 6, 7 \rightarrow 1100 \rightarrow E_{2} = 1 (to make it - odd partion)$  $E_{2} \rightarrow 1, 5, 6, 7 \rightarrow 1100 \rightarrow E_{2} = 1 (to make it - odd partion)$  $E_{3} \rightarrow 1, 5, 6, 7 \rightarrow 1100 \rightarrow E_{2} = 1 (to make it - odd partion)$  $E_{3} \rightarrow 1, 5, 6, 7 \rightarrow 1100 \rightarrow E_{2} = 1 (to make it - odd partion)$  $E_{3} \rightarrow 1, 5, 6, 7 \rightarrow 1100 \rightarrow E_{2} = 1 (to make it - odd partion)$  $E_{3} \rightarrow 1, 5, 6, 7 \rightarrow 1100 \rightarrow E_{2} = 1 (to make it - odd partion)$  $E_{3} \rightarrow 1, 5, 6, 7 \rightarrow 1100 \rightarrow E_{2} = 1 (to make it - odd partion)$  $E_{3} \rightarrow 1, 5, 6, 7 \rightarrow 1100 \rightarrow E_{2} = 1 (to make it - odd partion)$  $E_{3} \rightarrow 1, 5, 6, 7 \rightarrow 1100 \rightarrow E_{2} = 1 (to make it - odd partion)$  $E_{3} \rightarrow 1, 5, 6, 7 \rightarrow 0000 \rightarrow E_{2} = 1 (to make it - odd partion)$  $E_{3} \rightarrow 1, 5, 6, 7 \rightarrow 0000 \rightarrow E_{2} = 1 (to make it - odd partion)$  $E_{3} \rightarrow 1, 5, 6, 7 \rightarrow 0000 \rightarrow E_{2} = 1 (to make it - odd partion)$  $E_{3} \rightarrow 1, 5, 6, 7 \rightarrow 0000 \rightarrow E_{2} = 1 (to make it - odd partion)$

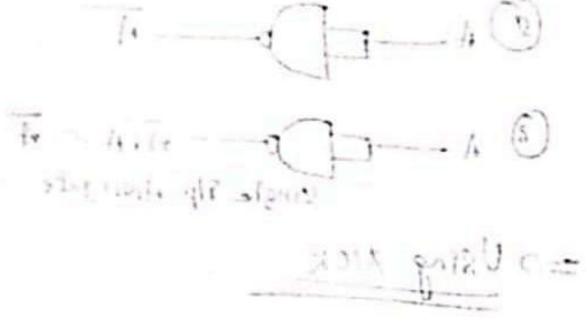

step 18 Determine the single error-Correctary code for the information code 10111 for odd paridy Bit E al m4+ mg Py m, mgt Pg PI P2 destination 23 22 2 Conver message set 20 Bit 2 6 4 3 8 Localgon m= 10111 Information 100 1000 011 0110 0101 0100 0011 0010 000) By USONG teast and eroor method Set we should fond pasiby fits Palliflets ? ŀ 0 ? 9 9 1: a= m 2PZ atpH Received 0 0 code Letp=1 2 2 5+1+1 2ミノメ  $P_1 \rightarrow P_1 m_1 m_2 m_4 m_5 = P_1 ||0|$ Letp=2 22 2 5+2+1 To make it become odd 22 2 8 X we kept p=0; so P, =0) Retp=3 23 2 5+3+1 2 P2m, m3my = P2110 To make it become 8≥9 X 24 > 5+4+1 Letp=4 ne leept P2=1; 50(P2=1 16 2 10 ~ P=> Py m2 m3 my = Py 110 To make It odd So, we need & parity sets. ne Kept Py=1 (Py=1) we should take parity sits always powers 9-2. P\_ Prm5 = Pr1 TO make It add we kept Ps=0 i (Ps=0) 20=1; 2=2, 2=4,2=8 24=16; 25=32 and soon. Error possition P& Pypp find the value to the paring = 0110 = 6 possition 23456789 Ilite # 9 bit hamming code 987654121 P1 P2 m1 P2 m2 m3 m P4 m5 P1P2 1 P3 1 1 0 P4 1 STOT 99 6 mposition (100011110

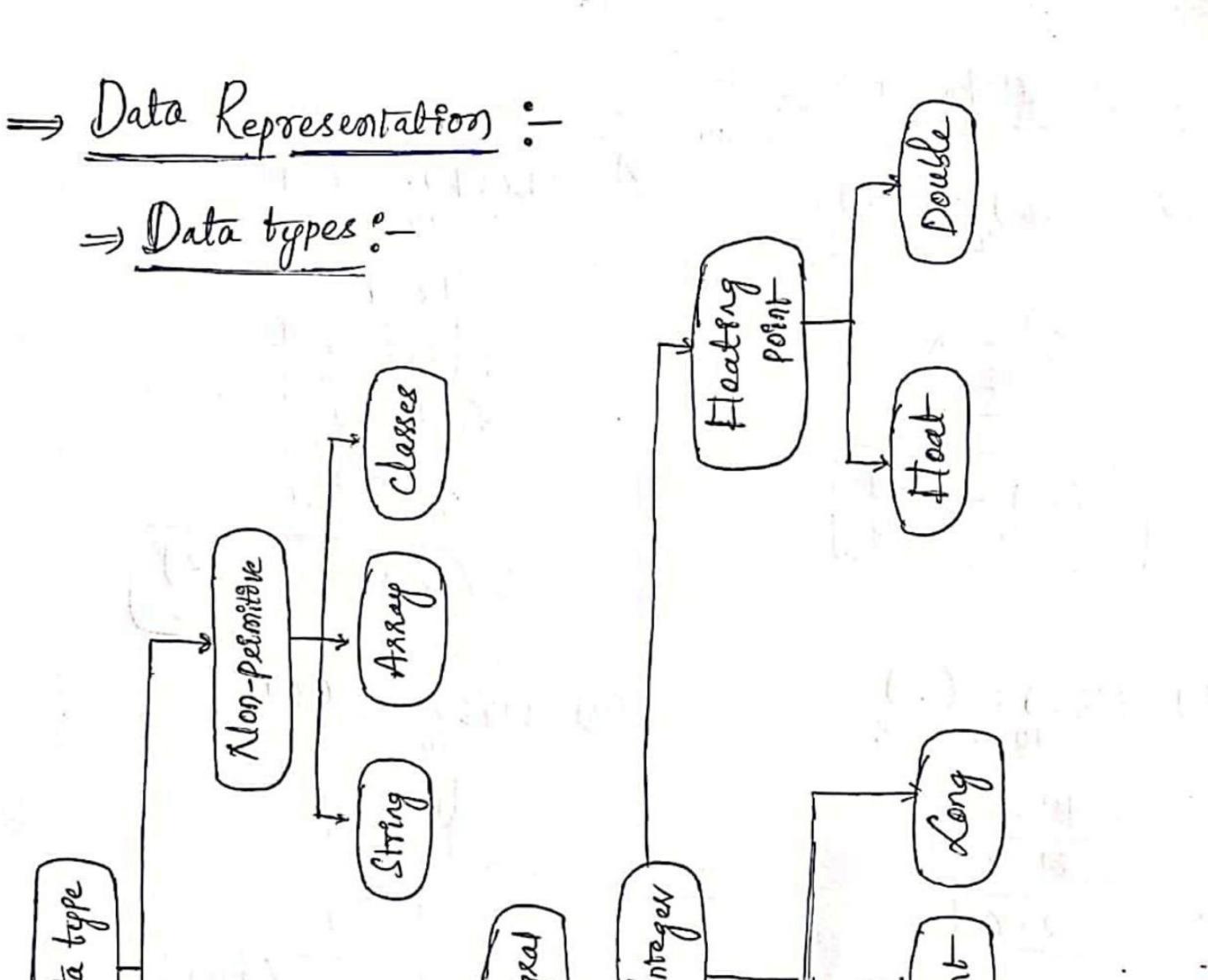

Integra ata) Ant Ant Numeric Chost Chasaeter Permittve Char Byte Boolean Boolean 1-5-

Decement to octal Q (?) 1234) (20) = (?) O 1234 8 8 20 154-2 2-4 2. "24) : (20) = i. (1234) = 2322 =(?) (?) 8 183) 3 (145) 83 8 8 8 18-22-8  $(145) = (221)_{10}$  $(183) = (267)_{8}$ => Fractional part:  $(27.625) = (?)_{8}$ O 0.625X8=5.000-95 8 27 0. 000 X 8 = 0.000 -> 0 3-3  $(a7.625)_{10} = (33.50)_{8}$

(3287. 5100098) = (?) (D Integer part Sol 0.5700098X8 = 4.0800 - 7 4 3287 0.0800 X 8 = 0.640 - 0 8 0.640 X 8 = 5.125->5 410-7 8 = 1.000 -> 1 . 81-2 0.125×8 6-3 : (3287.5100098) = (6327.4057) 3 (20.5) = (?) Freeboonal galt 820 0.5×8 = 4.0 -> 4 0.0X8 = 0.0-> 0

: (20.5) = (24.40)

$(60.7)_{0} = (?)_{8}$ 0.7×8=5.6-0.6×8 = 4.8 -> 4 60 0.8×8 = 6.4 -> 6 0.4 X8 = 3.2 -> 3 0.2×8 = 1.6 -> 1 (60.7) = (74.54631)

⇒ Decemal to Henadecimal °- (H=16) (1234) = (?)Ð (20) = (?)16/20 1 16 1234 16 77-2 4 - 13 (m) (20) = (14) $(1234)_{0} = (4D2)_{16}$  $(20.5)_{10} = (?)_{10}$ 3 H 0.5×16=8.0-38 16 20 0.0 × 16 = 0.0 - 0 1-4 : (20.5) = (14.8) (675.625) = C?) 675 16 0.625×16=10.000 -> 10 (02) A 16 42-3 0.000 × 16 = 0.000 -> 0 -10 or - (2A3.A) 16 (675. 625)

=> Binary to octal ?-To convert Grary to octal, starting from Strary point make georep of 3 sets and weste ste equévalent (2) (1101) = () (101) = (?) 001101 = 15 101->5 : (101) = (5)  $(101)_{a}^{2} = (15)_{a}^{2}$ ( ( onoiollo.11) = (?) 3 (10. 11001) = (?) 012010110.11 10.11001 110010 011010110 . 110 010.  $: (10.11001)_{2} = (2.62)$ : (011010110.11) = (226.6)  $(1101101.01101) = C_8$ 011010 200 T, J 3 2 101. : (1101201.01101) = (155-32)

$$= \frac{\text{Binaxy to Henadecemal :-}}{\text{To convext sinaxy to Henadecemal, Correct generation of the set of the se$$

16 2 ٠ 0010 1010 1111 1001 000100101011 10111000 10 00 F JE Ŷ L'II 11 (07) 12 2 2 9 (m) II :. (101001101011)]=(29AF)  $\frac{1}{2}(1001011.101110)_{2} = (128.88)_{16}$ 16 - Fim datt. ί×.

= Octal to other Number systems :-Octal to Decemal :-=)  $(24.4)_{g} = (?)_{10}$ (24) = (?) 0 2 41. 2 4 80 81 8 8° g1 2×8'+4×8° = 2×8'+4×8.+4×81 = 16+4 = 20 16+4.+4 21 : (24) = (20) 8 10 = 16+4.+0.5 = 20.5 10 (24.4) = (20.5) 10 P . ٢ (6327.4051) = (?) 8 = (?) (1234·242) = (), G

| 6  | 3  | 2  | 7  | • | 4  | 0    | 5 | $\left  \right $ |

|----|----|----|----|---|----|------|---|------------------|

| 83 | 82 | 81 | 80 | • | 81 | 1200 | 8 | 84               |

$$= 6x8^{3} + 3x8^{2} + 2x8^{1} + 7x8^{\circ} + 4x\frac{1}{8}$$

+  $0x + 5x + 5x + 1x1$

$82 + 8x + 84$

=  $3072 + 192 + 96 + 7. + 0.5100098$

= (3367.5100098)

16

$$= \frac{8}{668.440}$$

10.

=> Octal to Binary "- To convect actal to Gracy gest replace each actal deget by Str 3-SET Senarcy equivalent.

:.(561) = (10/11001)

:.(725) = (111010101)

(326) = (1) 8 2 3-2011 2 -> 010 6 -> 110

(226) = (011010110)

O(45a) = ()4 -> 100 5-> 101 2-> 010 : (452) = 100101010

=> Octal to Hendecemal ?- These is no direct conversion available for octal to benedecimal. to convert octal number into a heradecimal number by convectory outal to sonary them brareg to heradecimal (r) octal to decimal with decimal to Note:  $() \rightarrow () \rightarrow ()$   $() = () \rightarrow () \rightarrow ()$   $() = () \rightarrow () \rightarrow ()$   $() = () \rightarrow () \rightarrow ()$ benederinal. (1)  $(356.63) = C_{16}^{2}$ (2) (247.52) = C)16 step Octal to strateg Step Octal to Sinary Step @ lanary to Heradecinal step@ Borary to Heradeumal 3 5 6. 6 3 4 4 4 4 4  $011 101 110 \cdot 110 011$ 247.52 0000 0110 1110. 1100 1100

6000 1010 0111 1010 1000 =14 =14 (or) 7 10 (07) A ··(356.63) = (OEE.CC) : (247. 52) (0A7.48) Ξ encoderinal to other Number system " => Alenaderemants to Grang - $(2F9A)_{16} = ()_{2}$ 2 -> 0010 : (2F9A) = (001011111001000)2 E-> 1111 -) (00) 4 -> 1010

$(GA_3)_{lb} = C)_2$ 6-> ollo  $[:.(GA3)_{16} = (011010100011)_{2}$ 4 -> 1010 3 -> 00lj 3 (58C) = C)2 -5-> 010) :. (58c) = (010110001100) 8-> 1000 C-> 1100  $(GDE_3) = ()$ 7->011) D-> 1101 : (7DE3) = (011/110/1110001)) モー 1110 3-> 0011 Herederinal to Derimal " @ (SE.7A) = () (3A. 2F) = C) O E. 2 A 1601 LET 16 151 . 3×16 +10×16 + 2×11+15×162 SX16+14×16 +7×1 +10×1 161 62 = 48 + 10 + 2 + 15 = 90+14+0.43+0.03 = (104.46) · (3A·2F) = (58. 1836) : (SE.7A) = (104.46)

@ (ASC. BC7) = ()8

Heradecional to sinery

Brang to octal

> Complement q Numbers. (00) (0-1)'s complement and o's complement complements are used by systems to sampliby the Lubtraction operation base (radia) & system thereare two useful types q: complements, d's complement (Radia complement) and (I-1)'s complement (Diminished Redin complement). ⇒ Cr-D'x complement -For a given Neconber N' have me no. g digste n? belonging to 'r'number system, Men (8-1) complement (8-N)-) ts given by > o's complement. For a gaves number n'have the no. g desets '?? belonging to s'number system, then ols complement Es gives by 2-N

1's complement Benary > 2's complement 7's complement 8's compensat 9's complement Decimal (10) > los comprement 5/8 complement Headeenal (16)

=) 1/2 and 2/2 complements -The 1/2 complement q-a Strarge Number & Obtained complementing all stx lists, that is by replacing all 0/2 by 1/2 and all 1/2 by 0/2. Sa \*- O 0101101000 -> (Gaves Grange Number) 10100101111-> L 1/2 complement formy

> 16's compension

The 2's complement que Grang number & Ostained by. adding 1'to 9ts 1's complement. Sn= 01010000 - (Corres Grazep number) 101001011, -> (1/2 complement tors) III (adding 1) 1010011000 -> 2/2 complement => Brarep ædditsoo 0 + 0 = 00 + 1 = 1

$$(+0 = 1)$$

$$(+1) = 1 \quad 0 \rightarrow Sum$$

$$Carry \qquad Ump$$

$$(+1+1) = 1 \quad 1$$

$$Carry \quad Sum$$

$$(2) \quad 0 |10|0|0| \rightarrow Cerues brane presents$$

$$(20 \mid 0 \mid 0 \mid 0 \mid 0) \rightarrow U' = approlement = barm$$

= 1's complement Assumette -> In 1's complement subtraction, add the 1's complement 9 the Subtrahend to the Mouland. If there is a carrigout, being the carry around and add it to the Rep. Thes is called End around carry Look at the 188 80 bft (MSB). of these a O, the result is possibly and is true Grares. If MEB is i' the result is negetive and is is the 1's complement-form. Take Pts 1's complement and put ne \$450 to set magnitude In Grang.

D. Sasteast 4 from 25 088ng 8-181 Ascomplement of the Method. Sof Nomally 14-> 0000/110 00011001 complement [111000]  $-19 \longrightarrow 1111$ 0000 1010 1- Codding g-Kord assound carry) End around 0000 011 me M&B & B O' Lo me result P& possione and 5 80 pare strang. metafore, me regult is 00001011 = #11)

2) Add -25 to +14 Using 8-61-1's complement method 25-200011001 +14 -> 00001110 1111 18->11100110 -25-311100110 Complement -11 1110100 - NO carriej => Mere is no carry. me mere is a '1'. So, me result is Negative and is in 91ts 1's complement torm. Take 1's complement Producte re Rfsn => the complement of 11110100 & -00001011. The result 这一印。 (3) Ard -25 to -ly using 8-191 - 1's complement-method. 25 ) 00011001 (coma)

$$-25 \rightarrow 11100110 (Iscomplement) 14 \rightarrow 00001011 (none)$$

$$-14 \rightarrow 1111000 \text{ ord} (Iscomplement) 14 \rightarrow 00001011 (none)$$

$$-39 \qquad 11010010$$

$$Bid ontend 11010111 (adding q and onough carry) (1010111 (adding q and onough carry) (101011000) (arry) (101000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000) (1000)$$

Add tas to try cessing 8-191-11& complement arethinets ( I )+25 -> 00011001 A line in the second se +14 ---- 0000.001.0010 The second s +39 00/00/11 fill an east research maker income service and there is no carry - the mere of So, the result is possible and is so pure bonareg. Therefore, the result is 13910. EN:-D 1) Labteast 20 from 26 using 8-131-11/2 complement form 36 - 00100100 36-> 00/00/00 -: 20 -> 1110101) (Steomplement) 20-> 000/0100 +16 [100001111 End associated E ladding geord associat carry Carsoner 00010000 MSK IS 8 =) the MEB & Zero. The result is possitive and it is go Thee Snare form. 2 Add +36 to too Using 8-bit is complement form - 000 00 100 +36 >> 000/00100 > 000 10, 100 000 20. N8880 0017 1000 35

MSB-Es Zero. The result & posptine and 91-28 Patone binary form

Add -36 to -20 Using 8-69-11's complement form. 36-> 00100100 20-> 00010100 -36 -> 1/0/1011 - 1 stomplement -20 ->,11101011 - Hit -56 D. ( 1000110 adding quend ascurd carson orsound carry 11000111 MEB = => MSB & I the result is negative and it is in 1/8 complement

=> MSB & I the result is regarine and the simplement to the torm. To get the correct result take its complement to the result and pat we sign before the result.

1's complement -00111000 = -(56) 100011-Add -26 to too Using &-69t-1's complement form -36 10000 [10101] 36-> 00/00/00 +20 = E, 000 LO (00 20 - 00010100 110 MERSEI the MEB is 1'. meresalt is negative and it is by 18 complement form. ? Take 1's complement to the result and put nesses before the result  $1101111 \rightarrow -000/0000 = C10_{10}$

=) 2's complement - In 2's complement subtraction, add 28. complement que susteahend tomé mencend. If there is a cassepout, ignore it. If we mere is zero? The result is Possipire and is in true sinary form. If MSB is i' me result is regative and is in Pts 21/2 complement -form). subtract 14 from 25 using '8-691-218 complement aditionetic Sa-0

25-> 00011001 -14 -> 11110010 [100001011 grove of 1. Corseg mais More is a Carry isnore it. the marsiles of Co, me result is possive and is in normal sinery form. Therefore the result is + 0000/011 = +.17,0 D Add -25to +14 using 8-180 21s complement alltroportec

Statute the statute

Cerves the two benarge nambers X = LOLOLOO and Y=100001, perform lubtration (a) X-Y (b) Y-X Using 21 complements X = 1010100  $Y = 1000011 \rightarrow subtrahend$ 0111100  $\rightarrow 1k complement$ 0111101 -> 2/2 complement O Find 2k complement of suttachend D. Add suttochend to me monuend. 38

$$X = 1010100$$

$$Y = 0111101 \longrightarrow 21 \text{ complement } 9^{-1} \text{ Y}$$

$$(1) 0 0 0 0 0)$$

$$Dtscard \text{ mell} = 0$$

$$Carry \text{ mell} = 0$$

$$V = 1010100$$

$$(101011 \longrightarrow 11 \text{ complement})$$

$$Y = 1000011 \text{ X} = 1010100$$

$$0101011 \longrightarrow 11 \text{ complement}$$

$$Y = 1000011$$

ms=] There is no carry. And me MER Is 'I'lo me aiswer is 21s complement form. So find als complement of the result to get the correct ansires 000 -> lk complement 00 00/000/ Correctarsures als complement form

(Geven the two becares numbers X = 1010100 and Y=1000011, Performs the subtraction @ X-y and B Y-K using 18 complement (2) X=Y X = 1010100 =0111100 ->1's complement 7-Y 10010000 carren 0010001 MSB = 0 SO, It BE By toue Whatep form

V = 1000011  $X = 0101011 \rightarrow 1 \text{ k complement } q_{y}$  $\frac{1101110}{1018}$

> there is no corresp. And the MEB is I so the result is in its complement foors. So, find its complement of aiswer Is complement of 10110 K-00/0001

=> 9/2 and 10/2 complement? -> In gls complement subtraction just tollow the below rules O Find the gls complement of Riebtorehand and Add. 2/8 complement q subtrabend to minuend. If there is a carry It- Endrates that the answer is the they add carry to the LLD of the rescel to get quite answer. 3 If there is no carrier, It indicates that the one wer & negative and the result ostatined is its gk-complement Find the 9/2 complement quite following decimal number Q 4526.075 Ð 3465 782.54 9999.998 9999 4526.075 782. 3465 6534 217.45 5473.924 915 ausphone of J-3465) By very formula (104-3465)

9/2 complement Melled q Subtraction -Q subtract the following numbers using gls complement method 145.81-436.62 Step@ 999.99 ( i · · , 436.62 563.37 - 9/2 complement 9 436.62 stepe 745.81 563.37 30.9.18 (adding gundassound carry) 309 anene Carso ates the anewer 28 five 436.62-745.8) 999: step 145. 254.18 - 9/2 complement g 745.81 step 254.18 690.80

there is no carry, lo it indicating that the answer is heged put à mones bisn before pt. 998.99 690.80 - 309.19 -> therefore the aiswer is -203.18 I la wooplessent method q subtracted The tole complement que desined humber is ostabled by adding a 4' to Etz 9/2 complement and the lots complement of the following deconal number @ 782.54 (2) 4526-075-3465 9889.988 501 989.93 9899 4526-075 3465 782.54 5473.924 6534 217.45-)9/2 Complement complement 5473.925 6535-Juls 217:46 -1:10/5 compleant complement

(23) 1018 complement method q Sustaction p\_ 10 perform definal sulticetson Using 10/2 complement melhed, Ottalined the Ids complement q-the sustachend and odd to to the mirriend. If there is a carrier, I gude &t. the presence of the carrier > Endécates that the answer is possible. If metite no carrep, It-Indicates me answorks negative and the result Octained in Ptz 10/2 complement forms and put negociave says, infant g the answer-436.62-745.81 745.81-436.62 (2) ster@ 9,98.99 step ( 988.98 745-81 436.62 254. 563.37 254.19 563.38 Tiok. Complement form step@ 436.62 Step 🕑 745.81 254.19 562.38 ) no carry asswerts 69 0 .8 09 Igure me 988.98 carry endecates Step 3 6.9.0 .8 309.18 309.19

15's complement Method & find the 15k complement quie following numbers GAZG 15 15 15 SO (or) A 3 (-) 6A36 5 C 9 9509 (B) 9AD.3A 15 15 15.15 15 A D. 3 A 652.C5-) (issemplement) 6 9 Ists complement method of subtraction 69B-C14 15/2 complement of (-C14) stepD 15 15 15 ec 4-3 E B -> (15/2 complement q-(-c14) 69B-C14 = 69B+ (15ts complement-q EC14) (+) 3 E B (22) = (16) (+) 3 E B (22) = (16) A = 6 (24) 10 = (18) H

There is no very, result is () be

Step is complement of intermediate result is given by

$$15 + 15 + 15$$

$A + 8 - 6$

$5 - 7 - 9$

$16$

$16$

$16$

$16$

$16$

$16$

stept) 15k complement q-E69B)

4 -> 15k complement

step C14-69B = C14+ (15/2 complement-9-(-69B)) Cly  $(21)_{10} = (15)_{16}$ H 964 AND THE STOR 87 8 there is a carry 1 so the result as the carry 578 (End asound Carry) 579 : Finel result = + (579)

and the related to a second loss to

16 & complement method -First-fond the 15th complement and then add 1 & Fond the 16's complement of the following numbers ASC 15k complement is given by 15 15 15 CA 8 C 7 3 -> 15/s complement 5 16 & complement -> 573 574

100

「「いいい」のないのないのである

Step@:-

C9B - C1Y = C9B + (16'x complement 9 (C14))

(23) = (17)10 16 C9B 3 EC  $(24) = (18)_{16}$ D0 87  $(16)_{10} = (10)_{16}$ camp

there is a carry signore It. Sence the carry is 1. the result & Dive.

" Fonal result is + (087) 16.

(B) 2 A.4.2D - 3B2.3C

step 0 - 15k complement - 9- (-3B2.3C)

15 15 15. 15 15

$$-3 B 2 3 C$$

$$-C 4 D \cdot C 3 \rightarrow 15 \text{ b complement}$$

$$16 \text{ bs complement is given by,}$$

$$C 4 D \cdot C 3$$

$$1$$

$$C 4 D \cdot C 3$$

$$1$$

$$C 4 D \cdot C 4 \rightarrow 16 \text{ s complement}$$

$$step@$$

$$RA 4 \cdot 2D' - 3B2 \cdot 3C = 2A4 \cdot 2D + Clels complement - 2 - (-3B2 \cdot 3C)$$

$$2A4 \cdot R D$$

$$C 4 D \cdot C 4$$

$$EFI \cdot FT \rightarrow Shtermedsate result}$$

$$48$$

Company and and the state of th

Scanned with CamScanner

234.65-135.74 (@) Sol 7's complement q (-135.74) is given by 777.77 135.74 642.03 -37's complement : 234.65 + (7's complement q-(-135.74)) 234.65  $(8)_{0} = (10)_{8}$ 642.03 076.70 (carry =) residt is possive) 49 Scanned with CamScanne

076.70 (H) 76.71 (End around carry) So Result 18 +76. 11 B) 135.74-236.65 7's complement q (-236.65) is given by, 777.77 236.65 541.12 -> 7's complement 135.74-236.65 = 135.74 + (I's complement 9-(236.65)) 135.74 541.12 - (7/s complement) 677.06 Jutermedlate vesult there is no carry. Hence the final result is Give. Finel result is me 7/s complement of the above intermediate result 777.77 677.08 ". final result is 100.71

Subtract the following Using & & complement method: Ð 246.31-162.45 7's complement of (-162.45) is given by, 777.77 162.45 615.32 -> C7k complement) (H) 6 5.33 - ( 8ks complement) . 246.31-162.45 = 246.31 + (8's complement g-(162.45)) 246.31 フ 615.33 DO 63.64 Hence we result to (+) ve

correct Untere is a Carry Unertained we have

and ignore the coord .

S. Final recultes

$$+63.64$$

(B)  $162.45 - 246.21$

gis complement  $q - (-246.21)$  is given by,

$777.77$

(-)  $246.31$

$5731.46 \rightarrow (7k complement)$

$471$

$521.47 \rightarrow (8k complement)$

$$(162.45 = 246.31 = 162.45 + (81s complement q (-246.31))$$

$$\Rightarrow 162.45$$

$$531.47$$

$$714.14 \rightarrow (Intermediate result)$$

$$Were is no company. Hence the fonal result is () be. The state result is () be. The state$$

. Final result Is 63.64

=> Floating point Representation :the goal of floating point representation is representa large varge of numbers. En - Cervers the number -123. 154-×10 29:-Destance S/w two planet = 5-9×10 m logn = - (Negative) Mantelle = 123.154 mass of electron Eaponent = 5 Ð Base = 10 (decemal) - 9.1×10 900. En Geven the number 732. (36 × 10) CARD = + ( PORHAVE) Mantissa= 732.136

Caponent = Base = 10 (Decomal) 30 23 22 Eaponent(E) Fraction (F) 23 32-St-Single-preebsion Floating point Number 4.2\*10 ==> Eaponent : Only the mantiesa and emponent Montessa Base are stored. We base is implied (Already Known). It will save we memory.

$\mathcal{E}_{x^{o}} = (11.8) = (1011.11001...)_{2}$ Deceme representation 4 Eaponeal  $=(1.0111001) \times 2^{3}$ 12345 = 1. 2345 × 10 = (1.011100) 2 2 2 Rase mantissa Sesnificant-=) We will represent floating point numbers in single precision and double precession formats. They are shown below 31 30 2322 Stgn Enponent Manfilssa Montassa Emponent Sten ×-8502. < 151+> < 115ts-> 2 2(42 52-582 Single predsoon Double Preeiston 32-58 REEE stander d) 1 Sat for the Sagn (passtave Or Negative) \* 8 let for the range ( eaponent field) 23 Set for the precleson (feelson field)  $\int N = (-1)^{S} \times 1 \cdot feartson \times 2^{exponent-127} \quad 1 \leq exponent - 127$   $N = (-1)^{S} \times 0 \cdot feartson \times 2^{exponent-126}, exponent =$ -5254 E-127. \* Value = EI X(1+F) X2 Single Dreckston (r)

Fixed point Representation O A representation of real data type for a number that has a fixed number of digits affer the Neales point. Used to represent a limited Ð range of values. High performance (3) Less flexisle 9 × Real Number

Floating point Representation

A formulate representation of real numbers at an approximation to at to support a trade off Setween range and preetson.

Used to represent a wide rounge q-values.

Host performance

More flexiste

\* Limitation offloating points

Aze q mantassa is fined. floating Use a floating point Sol Flored point point format with a larger mantiesa. Clousle (\$355 ) long dousle (64 555) peosleme. Q what is the 111.11 indecinal what is 8.5 in Genary X 1111111.1111 @ 7.75 Ø 3 [000.0] Ø 0 7.375 0.00011 (8) 1000.10. 15-25 Ø

Ent -114.625. represent in Gratep 0.5 0.25 0.125 28 64 32 16 8 4 Sol 0010 0 | | 0.5+0.125 64+32+16+2=/141 133 in Genarg = 01110010.101 10000101 = 1.1100101×26-127 ·· 1,10000101,110010101. Sishyt 7.1. Exponent Maatissa Stan 1001010 11101000 0 0100 1010 1110 1000  $= (4AE_8)$ mon 14 404 representing floating point 19 32-Sits. Ear-0.000110011001100110011001100 128 6436 8421 1. 100 12001100 1100 1100 X24 0111011 SOL Enponent = -4+127= 123 Sign Sit = O Mantessa = 1001100/100 1100 1100 1100 Enporent (igt) mantissa (23 Sits) ٥ 10011001100110011001100. 0111011

→ Representation of Signed Sware numbers -Possitive numbers can be représented by unsigned numbers bowever to represent regitive numbers, we need notation for negative numbers. chere are two types & numbers. D Unsequed numbers D. Segued numbers (D unesqued numbers - there is no speetfector sign representation . The numbers without possesse (or) negative

Store ave known as unspend numbers. The Unspend numbers, are always possible numbers.

Depresentation . In signed numbers, the number may be possitive () negative. Different formats are used too representation signed benerg numbers. They are

Ciqued megnitude representation U Ð 1's complement representation (3)2/2 complement representation D'segn megnétiede representation -In segued magneticede form, an additional ist called the SAST 685 18 placed infront quite number. If the sagen bit & a °O', the number & possitive. If it is a '1', the number & vegetsve. = For snample :-

0101001 =+41 magnitude Signbold magnitade Sign bit In sten magnitude representation the mer represents the \$450 and remaining yoth represents the magnitude. (2) 1's complement representation. In 1/2 complement representation the possitive number remain . Unchanged. I's complement representation of negative neimber Can be ostained by the 1k complement - g the sensity number.

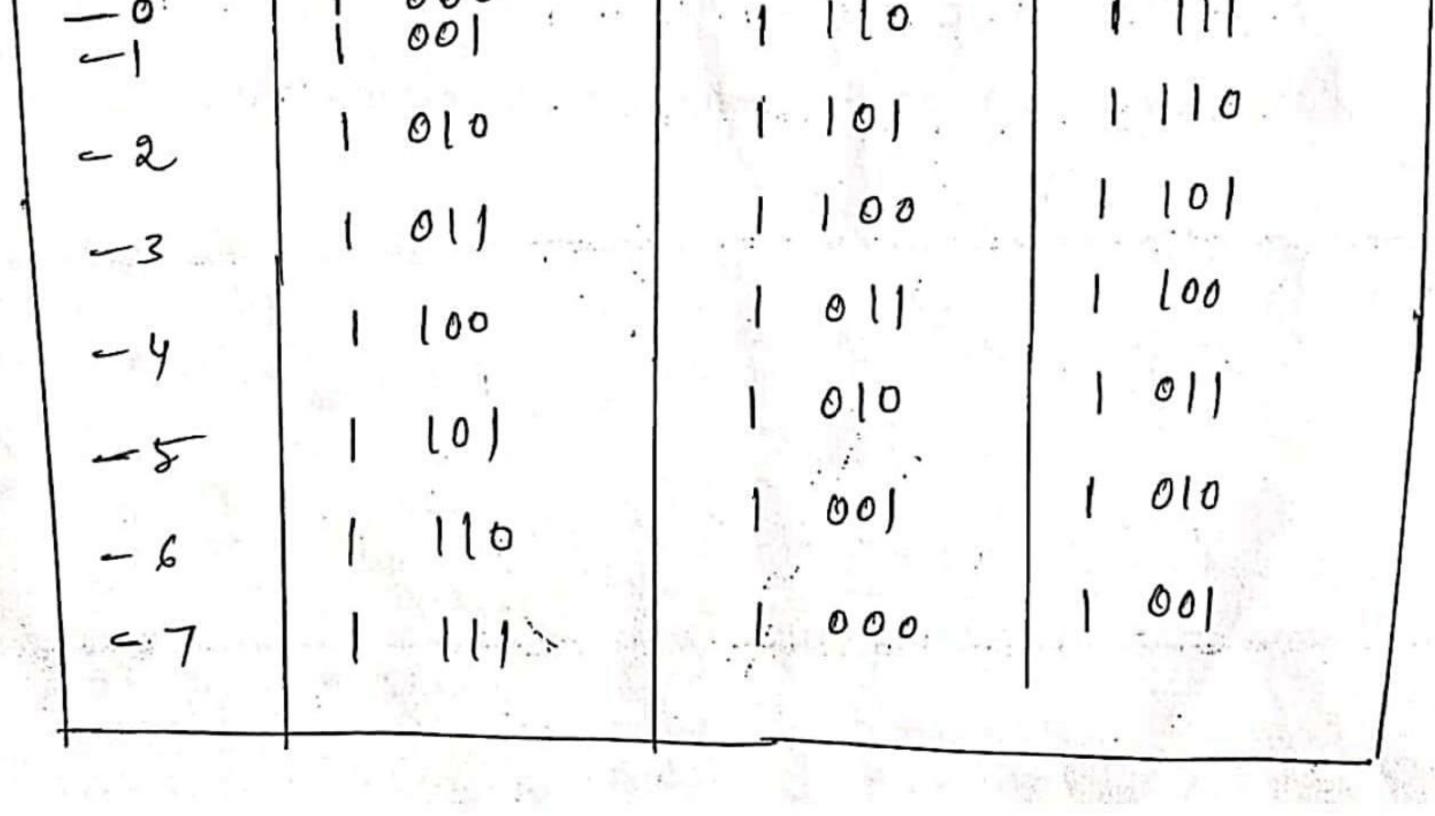

0 1 00 11 = + 51; MB = 0 for the spen bet 001100 = - 51; MeB = f for -re Stin 685 2 2's complement representation -In 2/2 complement representation, the positive numbers remain Unchanged, 2/2 complement representation & negative neorster can be altaEned by 1. Find the 1's complement of the mumber 2. To fond 21s complement que number adding "1" to 15 l'e complement number. 0110011 =+51 magnitude SASD 6ST 001101 = -57 / \$1 seen 2/2 complement form 7 magnatede Stan Sat Number systems Unsesned +1001 -100 8557595-01001 Sign magnitude Ston 41 1001

100)

0 100

0110

0111

0

Sign 1/2 complement

8850 2/8 complement

505-00

| Decemal | SPED magne tode | Stan 1 scomplement<br>form | Sagn 2/2 complement |

|---------|-----------------|----------------------------|---------------------|

| 44      | 011             | 0111                       | 0111                |

| 46      | 6 110           | : 0.110                    | 0 1 1 0             |

| 45      | 0 101           | 0 101                      | 0 [0]               |

| 44      | 0100            | . 0 100                    | 0. 00               |

| +3      | 0011            | 0 011                      | 0 011               |

| +2      | 0 010           | 0 010                      | 0 010               |

|         | 0 00            | 0 001                      | 0 00)               |

| +0      | 0 000           | 0 000                      | 0 000               |

Represent +51 and -57 Sign magneticale, Sign 1/2 complement and sangle complement representation.

- 81 1 110011 Spen Spt 580 681 Sen 1/2 complement 0 110011 1 001100 S850 587 Sren St 1 001101 SED 2's complement. 0110011 SBN 891-SP30 695-

- Represent +4x and -43 to Stan oragnitude, Span 1/8.

complement and 2's complement representations

+43 Sign magnitude LOLON 10101 SPEN 6AT 870 150 1 010/00 O LOLO M SASD 1's complement 890 895 S850 191-010101 Sigo 2's complement LOLOU SPSN 41 Stan 695, - anti-

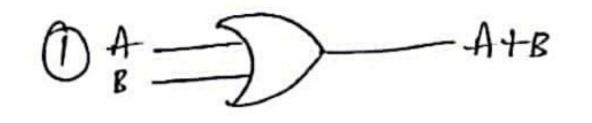

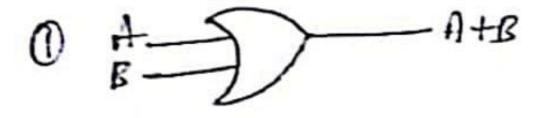

→ Combinational Circles :-Boolean Eapsessions - Boolean Algebra is a division of matter collicly deals with Operations on logic values and Encosporates Grasy variable. Boolean algebra was invented by gleat meltematicean George Boole in 1854. -> Minimization of Logic enpressions can be done by using -> Roolean algebra, Karnaugh map (K-map) are used for boolean theorems and Laws. -> INTE main moto of this concept is to make information limples, cheaper and Low cost. → Lagic Gates :- ① XIOF gate (05) Joventer :-Teutt table Y = AY=A A 4 0 Symbol 3 OR Gate -Y = A + BAND Gate -Y=AB Y=A+B B A-Y=AB в 0 0 0 A 0 : lliere 3 getes are permareg gates 0 0 C о 0 0. 0

|   | A | В | Y=AFB |

|---|---|---|-------|

|   | 0 | 0 | 1     |

|   | 0 | 1 | 0     |

| 1 | 1 | 0 | 0     |

| 1 | 1 | 1 | 0     |

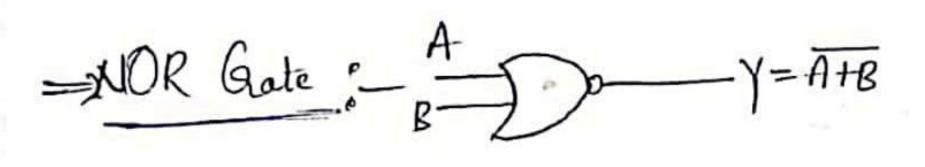

=> NAND Gate :- B \_\_\_\_\_ Y=AB : lice above two gates are universal gates

Y = AB A-В 0 0 1 0

Specal Grates -

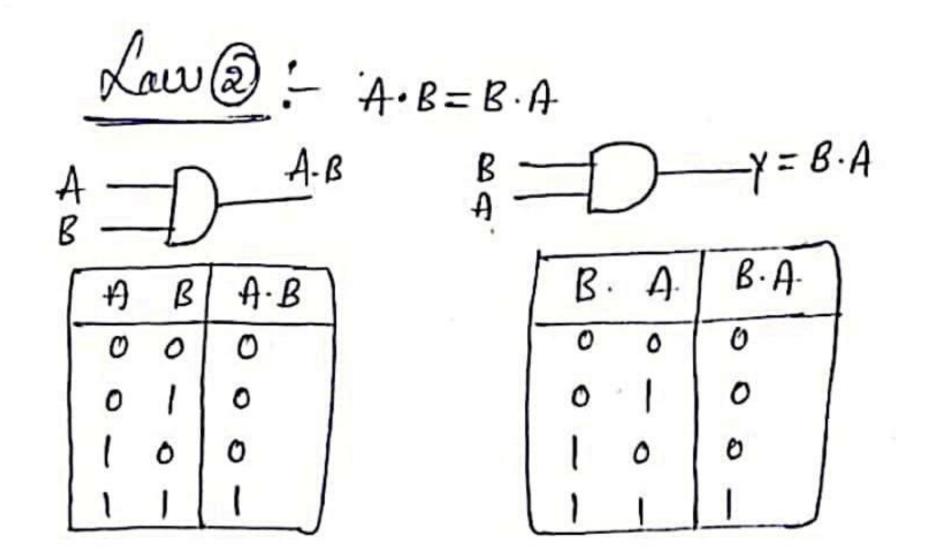

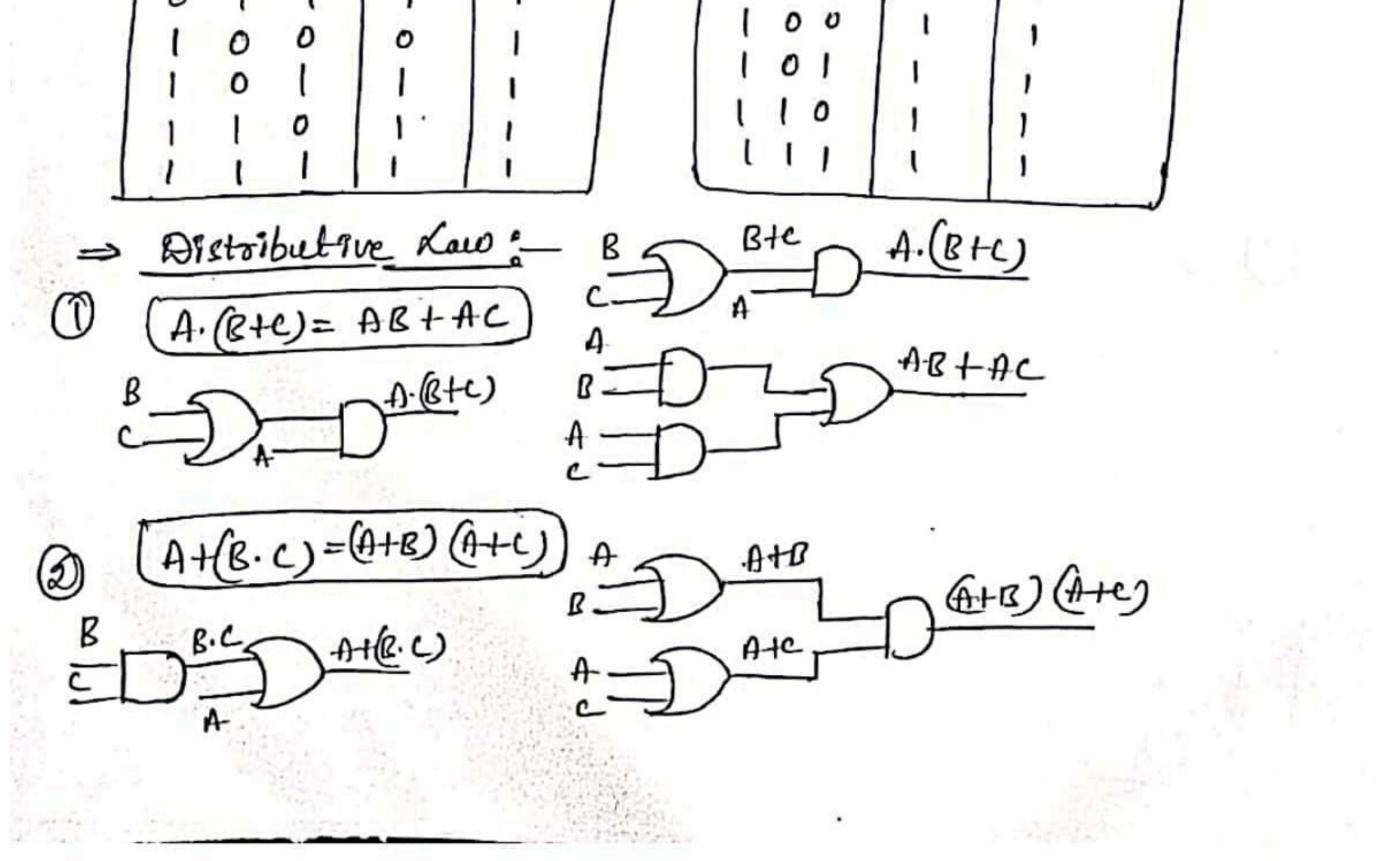

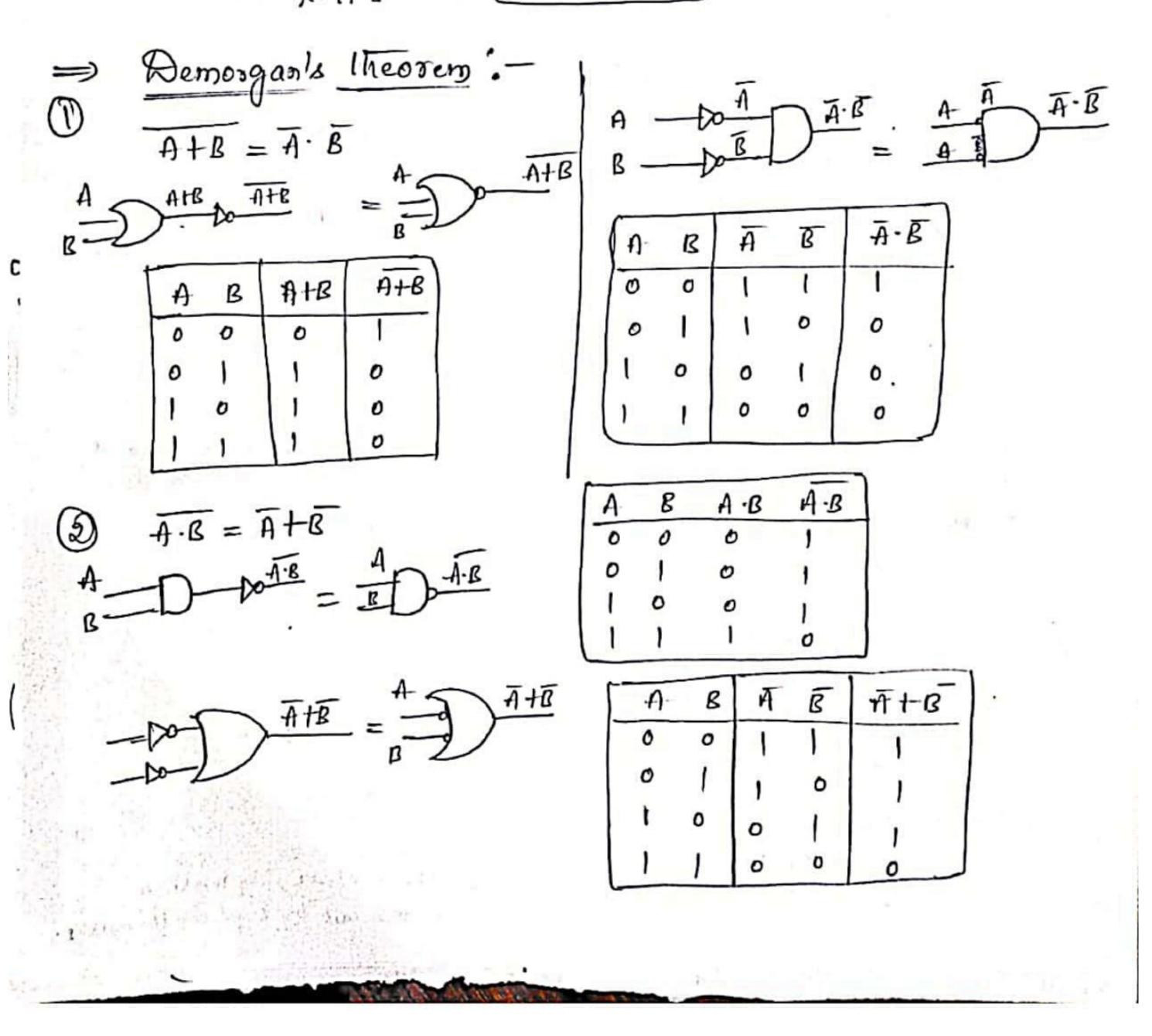

=> EX-NOR gate :-0 0 0 0  $\gamma = AOB$ =AB+AB > Laws of Boolean Algebre :-AND operation OR Operation 0.0 =0 Ŋ 0+0=0 5) 9) 0. ] = 0 2) 0+1=1 5) 1.0 = 0 10) 1+0=1 (ר 1. 1 = 1 1+1=1 4) 8)

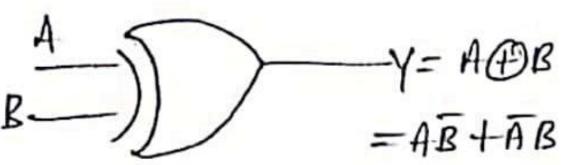

Y=ADB В A =) EX-OR gate ?-Ð O 0  $--Y = A \oplus B$ =  $A\overline{B} + \overline{A}B$ Y= AOB B A NOT operation

$$OR Kaw = -

A+0 = A

A+1 = 1

A+A = 1

A+A = 1

A+A = A

A+A = A$$

=) Commentative Law :--B y= B+A -1 A+B = B+A(1) B+A B A 0 0 4-0 Y=A+B O l 0 В AHB B A 0 0 ٥ ۱ 0 0

= Associative Law :-A+(B+C)=(A+B)+C)A+(B+C) Btck в\_ AtBtc (B+C) В A C 0 0 0 0 0 0 0 0 0 O

(A+B) (AHB)+C

(A+B)+C (++B) B C A O ٥ 0 0 ¢ 0 O 0 O 10

$$= \frac{Consensus Theorem}{} =$$

$$AB + \overline{A}C + BC = AB + \overline{A}C$$

$$AB + \overline{A}C + BC = AB + \overline{A}C$$

$$= AB + \overline{A}C + BC$$

$$= AB + \overline{A}C + BC(A + \overline{A}) \qquad \therefore A + \overline{A} = 1$$

$$= AB + \overline{A}C + BCA + BC\overline{A} \qquad [+C = 1]$$

$$= AB + \overline{A}C + BCA + BC\overline{A} \qquad [+C = 1]$$

$$= AB + \overline{A}C + BCA + BC\overline{A} \qquad [+B = 1]$$

$$= AB + \overline{A}C + BCA + BC\overline{A} \qquad [+B = 1]$$

$$= AB + \overline{A}C + BCA + BC\overline{A} \qquad [+B = 1]$$

$$= AB + \overline{A}C + BCA + BC\overline{A} \qquad [+B = 1]$$

$$= AB + \overline{A}C + BCA + BC\overline{A} \qquad [+B = 1]$$

$$= AB + \overline{A}C + BCA + BC\overline{A} \qquad [+B = 1]$$

$$= AB + \overline{A}C + BCA + BC\overline{A} \qquad [+B = 1]$$

$$= AB + \overline{A}C + BCA + BC\overline{A} \qquad [+B = 1]$$

Scanned with CamSca

Note:

()

$$AB + AB + AB + AB = AB$$

parantitiessis (Same no q-waitably are repeated ine magy

considered single term)

(2)  $A \cdot B \cdot E = A \cdot 0 = 0$ ; (3)  $AB \subset E = AB \cdot 0 = 0$

(3)  $AB \subset + AB \subset + AB \subset D$

$AB \subset + AB \subset + AB \subset D$

$AB \subset (HD) = AB \subset (D) = AB \subset C$

$= AB \subset (D+\overline{D})$

$= AB \subset (D+\overline{D})$

$= A+B[AC + BD + \overline{CD}]$

$= A+B[AC + BB + \overline{A}+BC]$

$= \overline{A}+BC + \overline{A}+BCRC$

$= \overline{A}+BC$

10

Sec. 1

AUDULE SUPPLYING

0

۱

AND AND AND

「「「ない」」「「「「「「「」」」

and the second se

$$E_{n} := F(A_{1}B_{1}C) = TT(M_{1} + M_{2} + M_{6}, M_{7})$$

=  $TTM(4, 2, 6, 7)$

$$=) \text{ Standard pos form } = 11 \text{ we form } \text{ s also called as conjunctive} \\ \text{ Canon } \text{ call form } (CCF) \\ \text{SN}_{-} = f(A_1B_1c) = (\overline{A}+\overline{a}) (A+B) \\ = (\overline{A}+\overline{a}+c.\overline{c}) (A+B+c.\overline{c}) (i.c.\overline{c}=0. \\ = (\overline{A}+\overline{a}+c) (\overline{A}+B+c) (A+B+c) (A+B+c) \\ \text{SN}_{-} = (onvert \ \text{Sop} + n \ \text{Strandard } \text{sop} - form \\ f(A_1B_1c) = A(C+AB+Bc) \\ \text{SN}_{-} = A(B+\overline{a})C + AB(C+\overline{c}) + (A+\overline{a})BC \\ \text{SN}_{-} = A(B+\overline{a})C + AB(C+\overline{c}) + (A+\overline{a})BC \\ \text{SN}_{-} = A(B+\overline{a})C + AB(C+\overline{a})BC \\ \text{SN}_{-} = ABC+A\overline{B}c + ABC+AB\overline{c} \\ \text{SN}_{-} = ABC+A\overline{B}c + \overline{ABC} + AB\overline{c} \\ \text{SN}_{-} = ABC+A\overline{B}c + \overline{ABC} + \overline{ABC} \\ \text{SN}_{-} = ABC+A\overline{B}c \\ \text{SN}_{-} = ABC+A\overline{B}c + \overline{ABC} \\ \text{SN}_{-} = ABC+A\overline{B}c \\ \text{SN}_{-} = ABC+A\overline$$

| Decend | ABC     | minterms      | Masterme   |

|--------|---------|---------------|------------|

| 0      | 000     | ABC (mo)      | A+B+C(MO)  |

| 1      | 001     | ARC (m1)      | A+B+T(MI)  |

| 2      | 010     | ABE (m2)      | AtB+C(M2)  |

| 3      | 011     | ARC (m2)      | A+B+E (M3) |

| 4      | 100     | ABE (my)      | A+B+C (Mu) |

| 5      | 1.0.1   | ABL (MS)      | A+B+E(M5)  |

| 6      | 1.10    | ABE (MG)      | Ā+B+c (M6) |

| 7      | I had I | ABC (m)       | A+E+E(M7)  |

|        |         | 1 100 alter a |            |

「「ころいい」

ř.

٠

Rules for K-map minimization -Eilher group zeros & ones  $^{(1)}$ Diagonal mapping is not allowed Ð Only power of 2, no. g colle & each group [ie 2, 4, 6, 8....) 3 Group should be as large as possible Ò overlapping is allowed. ٢ 2-valiable K-map Deoslems on K-map representation (gop)  $(in, f(n_1 B) = (0, 3)$ U, f= ARTAB + AR 1, f= AB+AB B R 7B A O A Ā A A = AB + AB. = (A+B)  $P(A_1B_1C) = Sm(3,4,6,7)$ A to AB CHABL + ABC + ABC + ABC + ABC A BC DO OI BC BE BC BE BC BL BE BC A D

| $\cap$                                           |                                                                             |

|--------------------------------------------------|-----------------------------------------------------------------------------|

| Of convert the following in the                  | Ssop form and calculate                                                     |

| the minterne                                     | 0                                                                           |

| (a) $f(A B) = \overline{A}B + B$                 | (B + (MB,C) = ABT + ABC + AB                                                |

| Set siven FAIR) = ABHR                           | = ABE + ABC + AB()                                                          |

| $=\overline{AB}+RU$                              | =ABC + ABE + AB(C+Z)                                                        |

| = AB+B(A+A) 1: A+A=1                             | = ABC + ABC + ABC + ABC (:: c+c=1)                                          |

| = AB + AR + AB (:. AR + AB= AB<br>91-same digita | $= m_{\ell} + m_{s} + m_{s} + m_{s}$                                        |

| = ABTAR are more thing                           | It-should be in people Order                                                |

| laccome DAC 1                                    |                                                                             |

| $= m_1 + m_3$<br>= $\varepsilon m(l_1 3)$        | $: m_{2} + m_{c} + m_{c} + m_{J}$ $\Rightarrow \Sigma m (3, S_{j} (S_{j}))$ |

| 1                                                |                                                                             |

| Q convert the following in the sport             | S-formand Calculate the                                                     |

| much legiss.                                     |                                                                             |

$F(A_{1}B) = A(\overline{A} + \overline{B}) = A(\overline{A} + \overline{B}) B = A$

$= A + o (\overline{A} + \overline{E})$   $= A + (\overline{E} \cdot \overline{E}) (\overline{A} + \overline{E})$   $= (\overline{A} + \overline{E}) (A + \overline{E}) (\overline{A} + \overline{E})$   $= (\overline{A} + \overline{E}) (A + \overline{E}) (\overline{A} + \overline{E}) (\overline{A} + \overline{E})$   $= (\overline{A} + \overline{E}) (A + \overline{E}) (\overline{A} + \overline{E})$   $= (\overline{A} + \overline{E}) (A + \overline{E}) (\overline{A} + \overline{E})$   $= (\overline{A} + \overline{E}) (A + \overline{E}) (\overline{A} + \overline{E})$   $= (\overline{A} + \overline{E}) (A + \overline{E}) (\overline{A} + \overline{E})$   $= (\overline{A} + \overline{E}) (A + \overline{E}) (\overline{A} + \overline{E})$   $= (\overline{A} + \overline{E}) (A + \overline{E}) (\overline{A} + \overline{E})$   $= (\overline{A} + \overline{E}) (A + \overline{E}) (\overline{A} + \overline{E})$   $= (\overline{A} + \overline{E}) (A + \overline{E}) (\overline{A} + \overline{E})$   $= (\overline{A} + \overline{E}) (A + \overline{E}) (\overline{A} + \overline{E})$   $= (\overline{A} + \overline{E}) (A + \overline{E}) (\overline{A} + \overline{E})$   $= (\overline{A} + \overline{E}) (A + \overline{E}) (\overline{A} + \overline{E})$   $= (\overline{A} + \overline{E}) (A + \overline{E}) (\overline{A} + \overline{E})$   $= (\overline{A} + \overline{E}) (A + \overline{E}) (\overline{A} + \overline{E})$   $= (\overline{A} + \overline{E}) (A + \overline{E}) (\overline{A} + \overline{E})$   $= (\overline{A} + \overline{E}) (A + \overline{E}) (\overline{A} + \overline{E})$   $= (\overline{A} + \overline{E}) (A + \overline{E}) (\overline{A} + \overline{E})$   $= (\overline{A} + \overline{E}) (A + \overline{E}) (\overline{A} + \overline{E})$   $= (\overline{A} + \overline{E}) (A + \overline{E}) (\overline{A} + \overline{E})$   $= (\overline{A} + \overline{E}) (A + \overline{E}) (\overline{A} + \overline{E})$   $= (\overline{A} + \overline{E}) (A + \overline{E}) (\overline{A} + \overline{E})$   $= (\overline{A} + \overline{E}) (A + \overline{E}) (\overline{A} + \overline{E})$   $= (\overline{A} + \overline{E}) (A + \overline{E}) (\overline{A} + \overline{E})$   $= (\overline{A} + \overline{E}) (A + \overline{E}) (\overline{A} + \overline{E})$   $= (\overline{A} + \overline{E}) (A + \overline{E}) (\overline{A} + \overline{E})$   $= (\overline{A} + \overline{E}) (A + \overline{E}) (\overline{A} + \overline{E})$   $= (\overline{A} + \overline{E}) (A + \overline{E}) (A + \overline{E})$   $= (\overline{A} + \overline{E}) (A + \overline{E}) (A + \overline{E}) (A + \overline{E})$   $= (\overline{A} + \overline{E}) (A + \overline{E}) (A + \overline{E}) (A + \overline{E})$   $= (\overline{A} + \overline{E}) (A + \overline{E}) (A + \overline{E}) (A + \overline{E})$   $= (\overline{A} + \overline{E}) (A + \overline{E}) (A + \overline{E}) (A + \overline{E})$   $= (\overline{A} + \overline{E}) (A + \overline{E}) (A + \overline{E}) (A + \overline{E})$   $= (\overline{A} + \overline{E}) (A + \overline{E}) (A + \overline{E}) (A + \overline{E})$   $= (\overline{A} + \overline{E}) (A + \overline{E}) (A + \overline{E}) (A + \overline{E}) (A + \overline{E})$   $= (\overline{A} + \overline{E}) (A + \overline{E}) (A + \overline{E}) (A + \overline{E})$   $= (\overline{A} + \overline{E}) (A + \overline{E}) (A + \overline{E}) (A + \overline{E})$   $= (\overline{A} + \overline{E}) (A + \overline{E}) (A + \overline{E}) (A + \overline{E})$   $= (\overline{A} + \overline{E}) (A + \overline{E}) (A + \overline{E}) (A + \overline{E}) (A + \overline{E})$   $= (\overline{A} + \overline{E}) (A + \overline{E}) (A + \overline{E}) (A + \overline{E}) (A + \overline{E})$   $= (\overline{A} + \overline{E}) (A + \overline{E}$

$= (A + B \cdot \overline{E}) (A + \overline{B}) (B + A \cdot \overline{A})$   $= (A + B) (A + \overline{B}) (B + A \cdot \overline{B}) (B + A) (B + \overline{A})$   $= (A + B) (A + \overline{B}) (A + \overline{B}) (A + \overline{B}) (\overline{A} + B)$   $= (A + B) (A + \overline{B}) (\overline{A} + B) (\overline{A} + B) (\overline{A} + B)$   $= (A + B) (A + \overline{B}) (\overline{A} + B) (A + \overline{B}) (\overline{A} + B)$   $= (A + B) (A + \overline{B}) (\overline{A} + B) (A + \overline{B}) (\overline{A} + B) (\overline{A} + B)$   $= (A + B) (A + \overline{B}) (\overline{A} + B) (\overline{A} + B) (\overline{A} + B) (\overline{A} + B)$   $= (A + B) (A + \overline{B}) (\overline{A} + B) (\overline{A} + B) (\overline{A} + B) (\overline{A} + B)$   $= (A + B) (A + \overline{B}) (\overline{A} + B) (\overline{A} + B) (\overline{A} + B) (\overline{A} + B)$   $= (A + B) (A + \overline{B}) (\overline{A} + B) (\overline{A} + B) (\overline{A} + B) (\overline{A} + B)$   $= (A + B) (A + \overline{B}) (\overline{A} + B) (\overline{A} + B) (\overline{A} + B) (\overline{A} + B)$   $= (A + B) (A + \overline{B}) (\overline{A} + B) (\overline{A} + B) (\overline{A} + B)$   $= (A + B) (A + \overline{B}) (\overline{A} + B) (\overline{A} + B) (\overline{A} + B)$   $= (A + B) (A + B) (A + B) (\overline{A} + B) (\overline{A} + B)$   $= (A + B) (A + B) (A + B) (\overline{A} + B) (\overline{A} + B)$   $= (A + B) (A + B) (A + B) (A + B) (\overline{A} + B) (\overline{A} + B)$   $= (A + B) (A + B) (A + B) (A + B) (\overline{A} + B) (\overline{A} + B)$  = (A + B) = (A + B) = (A + B) = (A + B) = (A + B) = (A + B) = (A + B) = (A + B) = (A + B) = (A + B) = (A + B) = (A + B) = (A + B) = (A + B) = (A + B) = (A + B) = (A + B) (A

Note: K-map constst of a no. of Squareq. Each one q-live Square Is coll. To do K-map intrimization like expression shows be to sop from (2) pos form. Itile is entremely weber and entensingly used in the minimization of function of 2, mesagle K-map, z-variagle K-map, 4- variagle K-map and 2007.

f= MM(0,2,3, 4,5,6,7,9,149) Q F(AIB)=(A+B)(A+B) E ありごというが 0 Ato Cto 6+5 EtD R C+5 C+D 0 14 4 0 AtB 0 0 0 B=f 0 0 AHB 0 ٥ 0  $f(A_1B_1C) = (A+B+C)(\overline{A}+\overline{B}+\overline{C})$   $(A+B+C)(\overline{A}+\overline{B}+\overline{C})$ AIB (0 0 ٠ AIB Bti Bte Bte Btc (C+D) (A+B+C) (AIB+C) (A+E) 0 0 (0 > (E+E) A f= (2+0). (A+12+c) (A+15+c) (A+0) 0 A V(A+B)

( ) may it no de alla alla in l'alla l'alla 149113 1.1.2.2 26 XJAND and NOR Implementation of In the design of digital circents, the minimal boolean expressions are usually obtained in sop -form (er) pos form. Sometimes the minimal enpressions may also be enpressed in hybrid -form. For example -f= ABC + ABC + ABC 1 (F)Given enample is in sop-form. So, sop enpoussion can be implemented by using AND OR Logic as shown below. (1)Lording (ad hidy ABC (15 (S)9512 (1 1) 1239 D supris pl -ABC+AB+ABC 2anil. AB Replace 325 1 E Commerle mensle Marinelle

Scanned with CamScanger

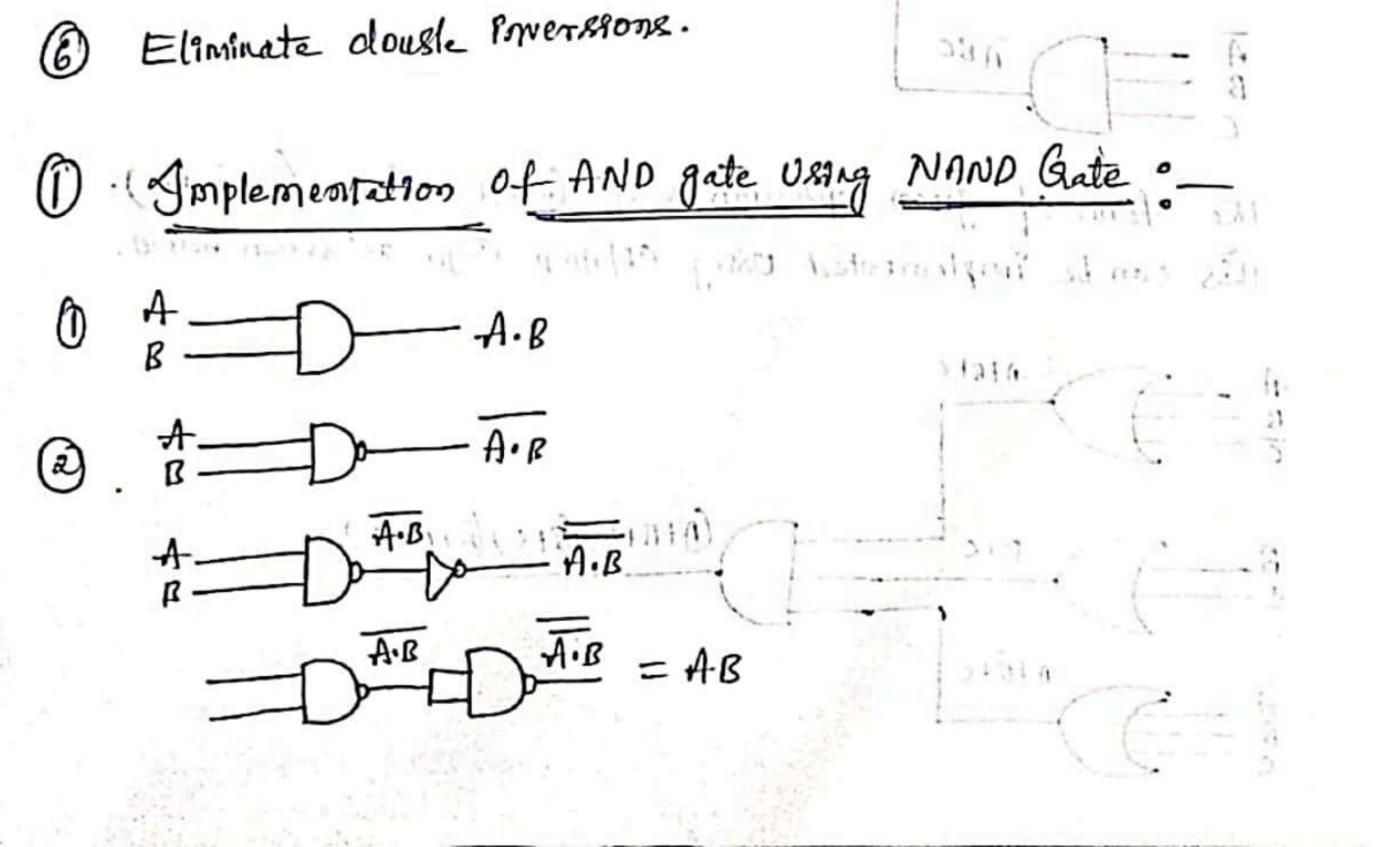

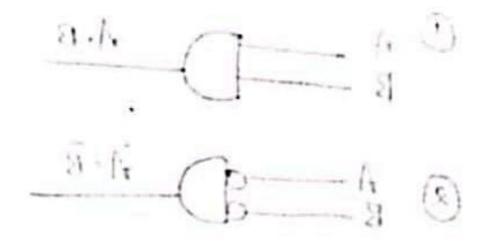

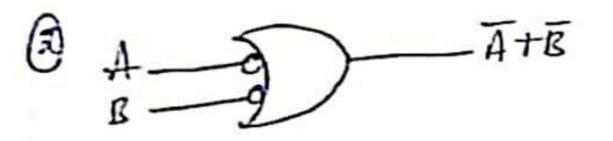

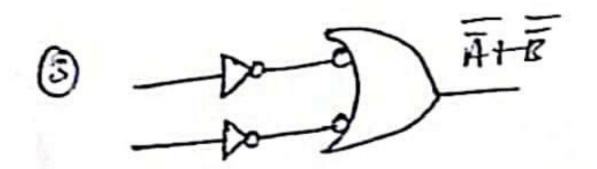

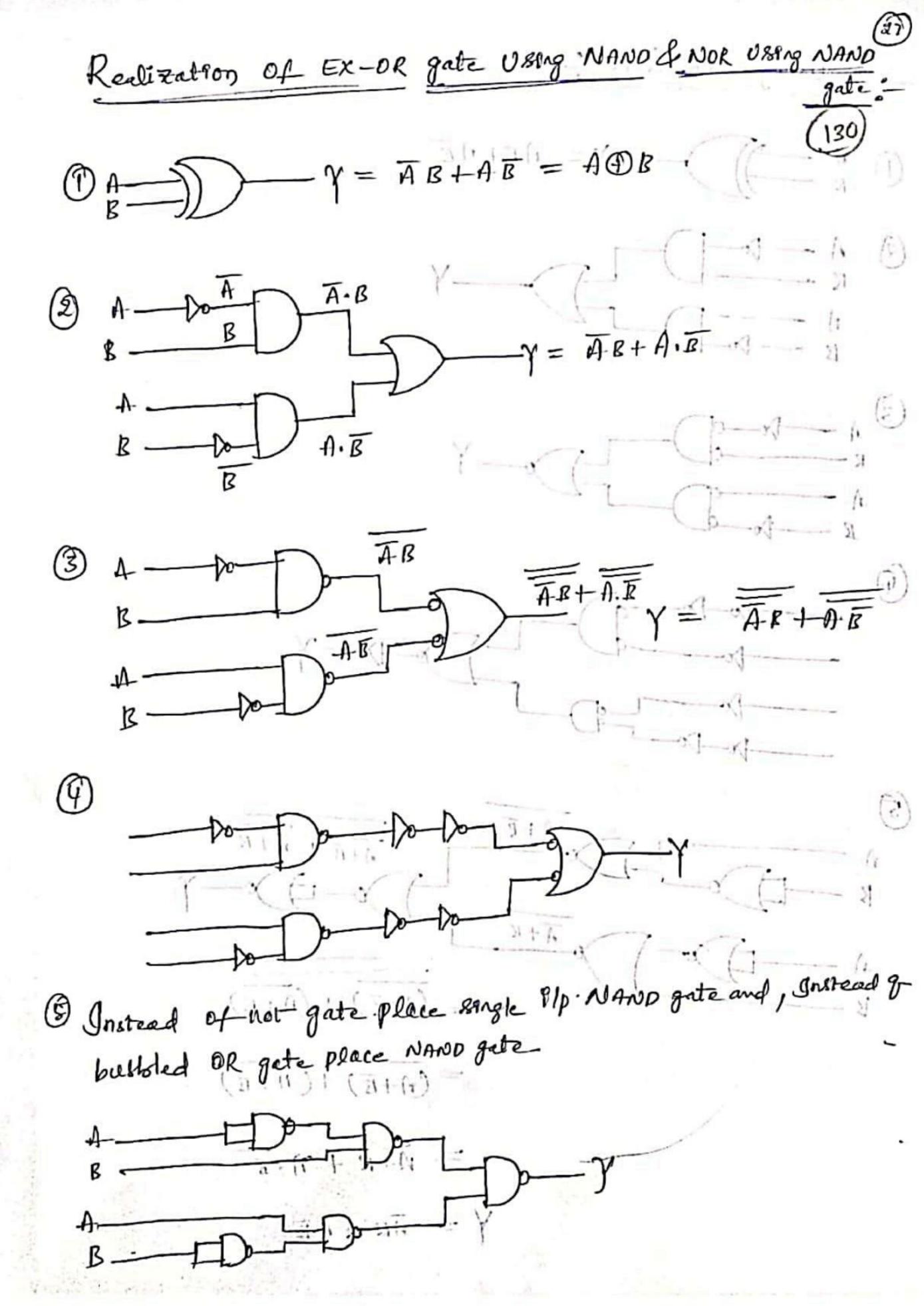

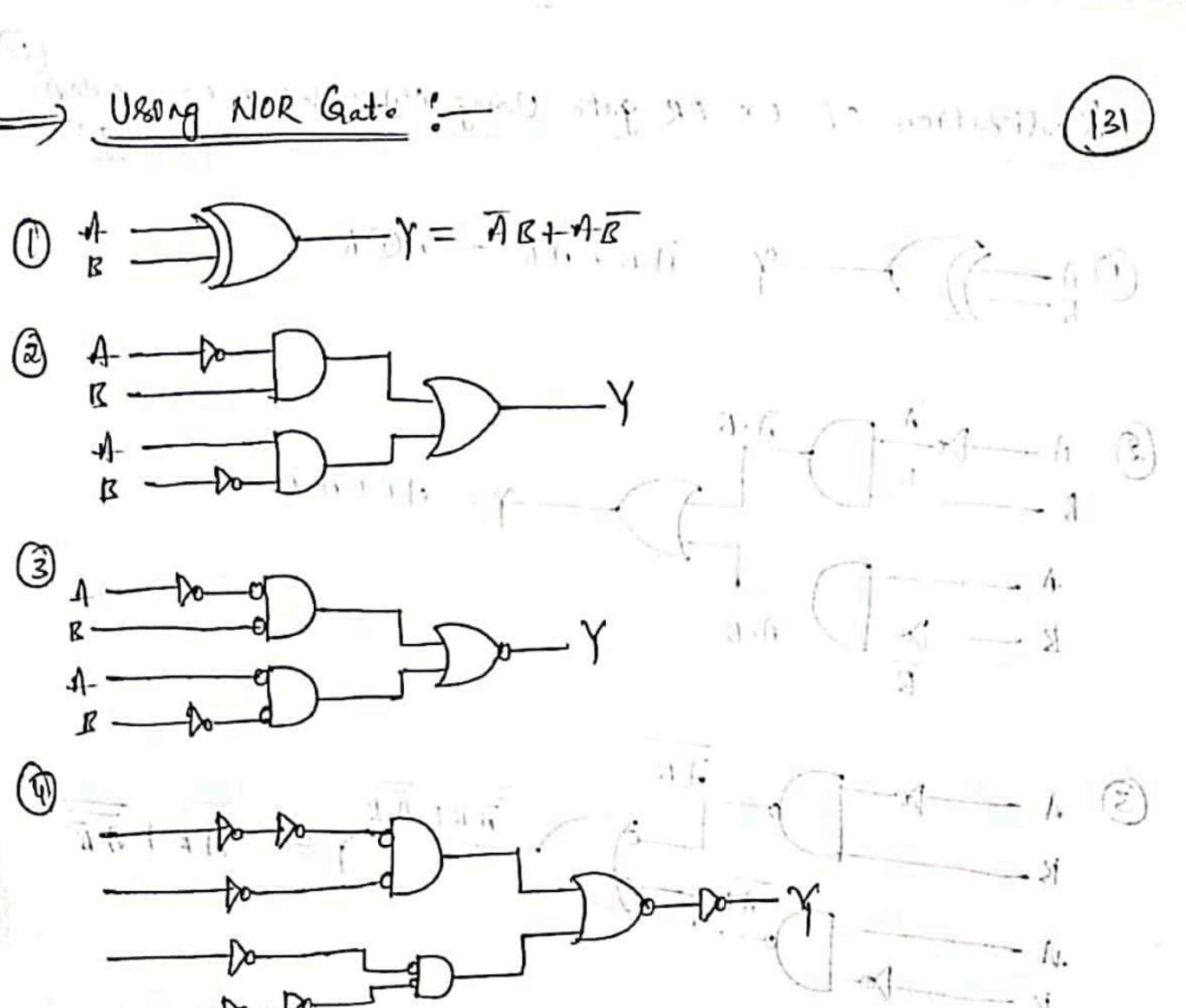

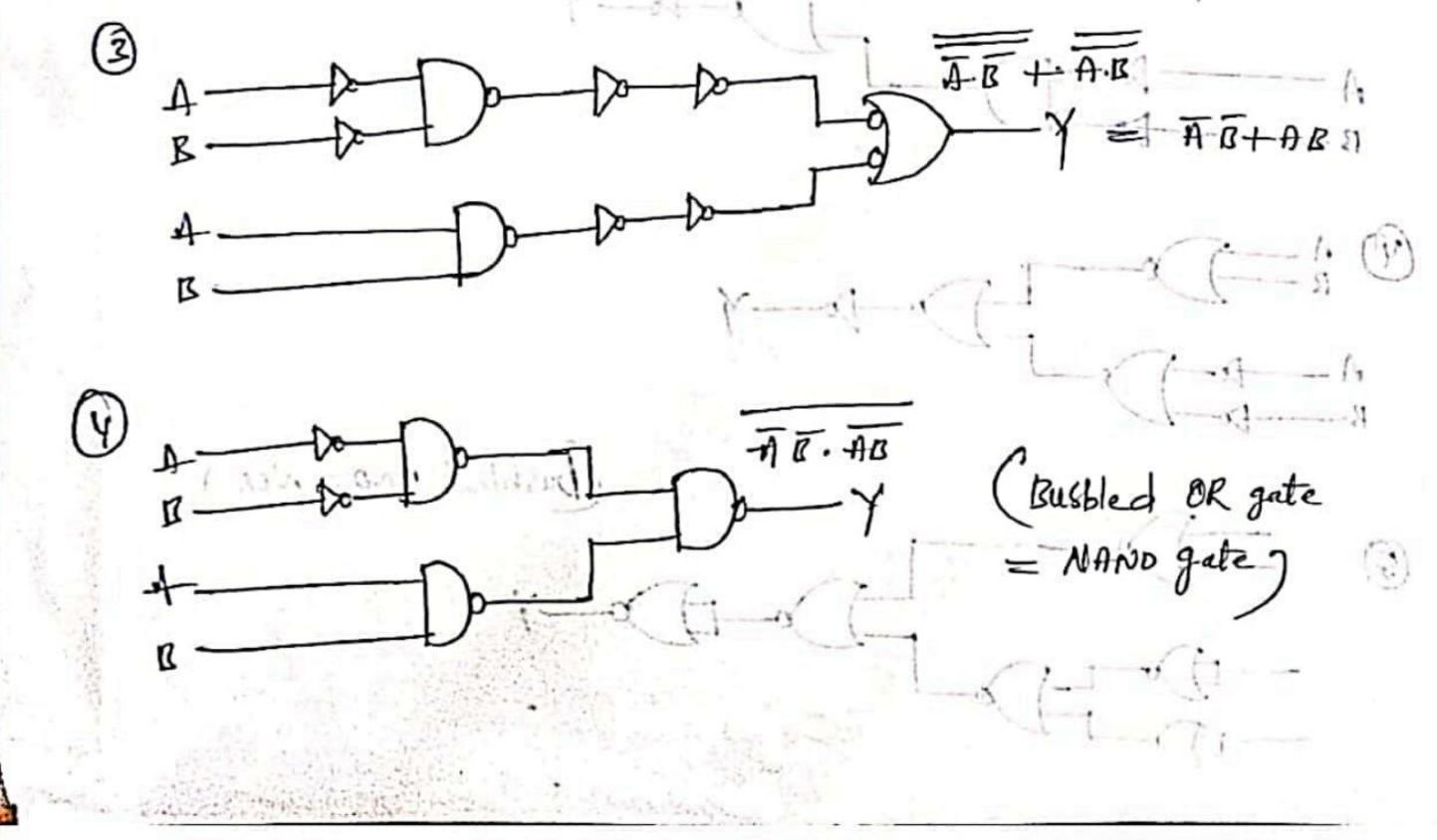

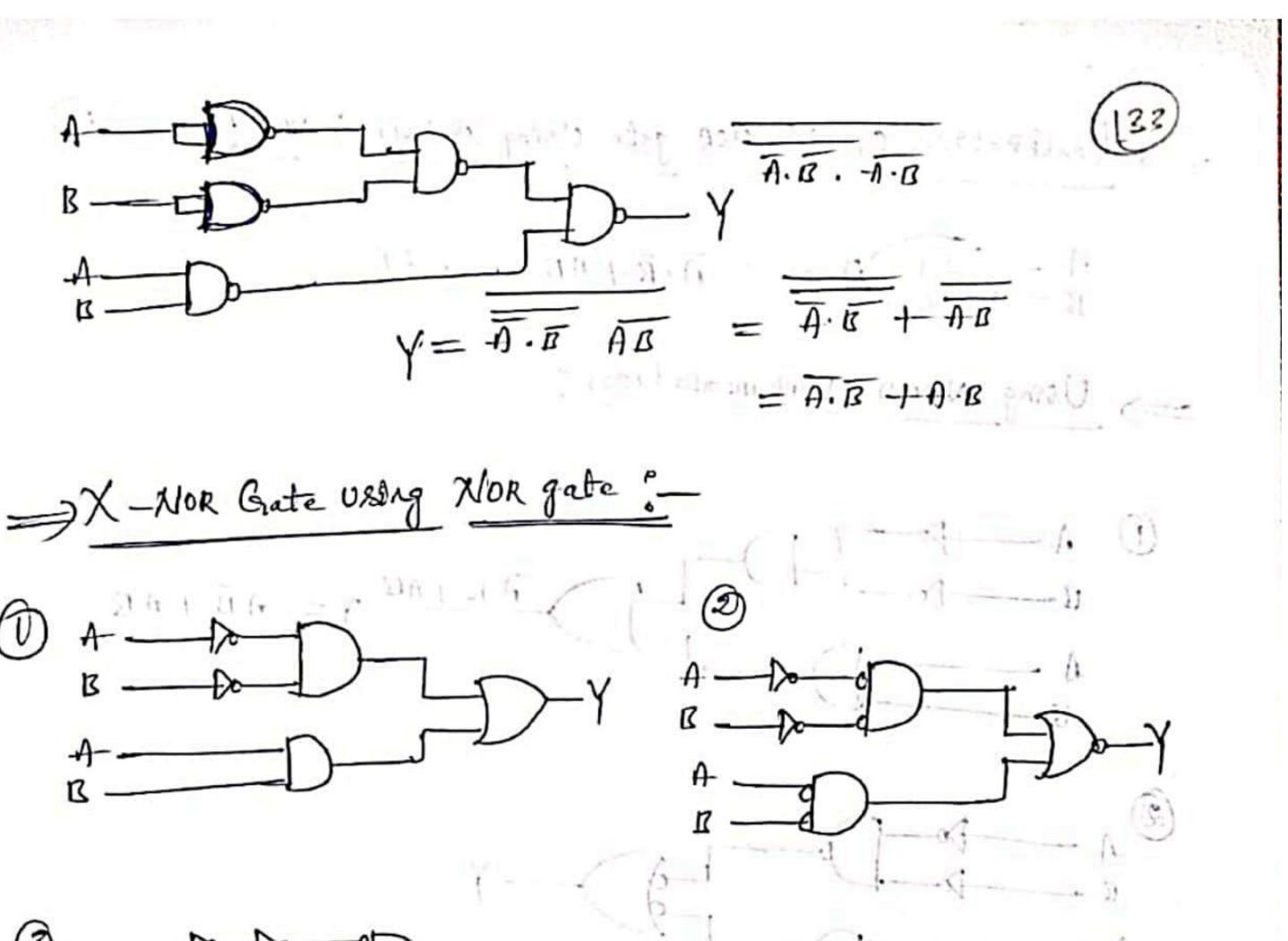

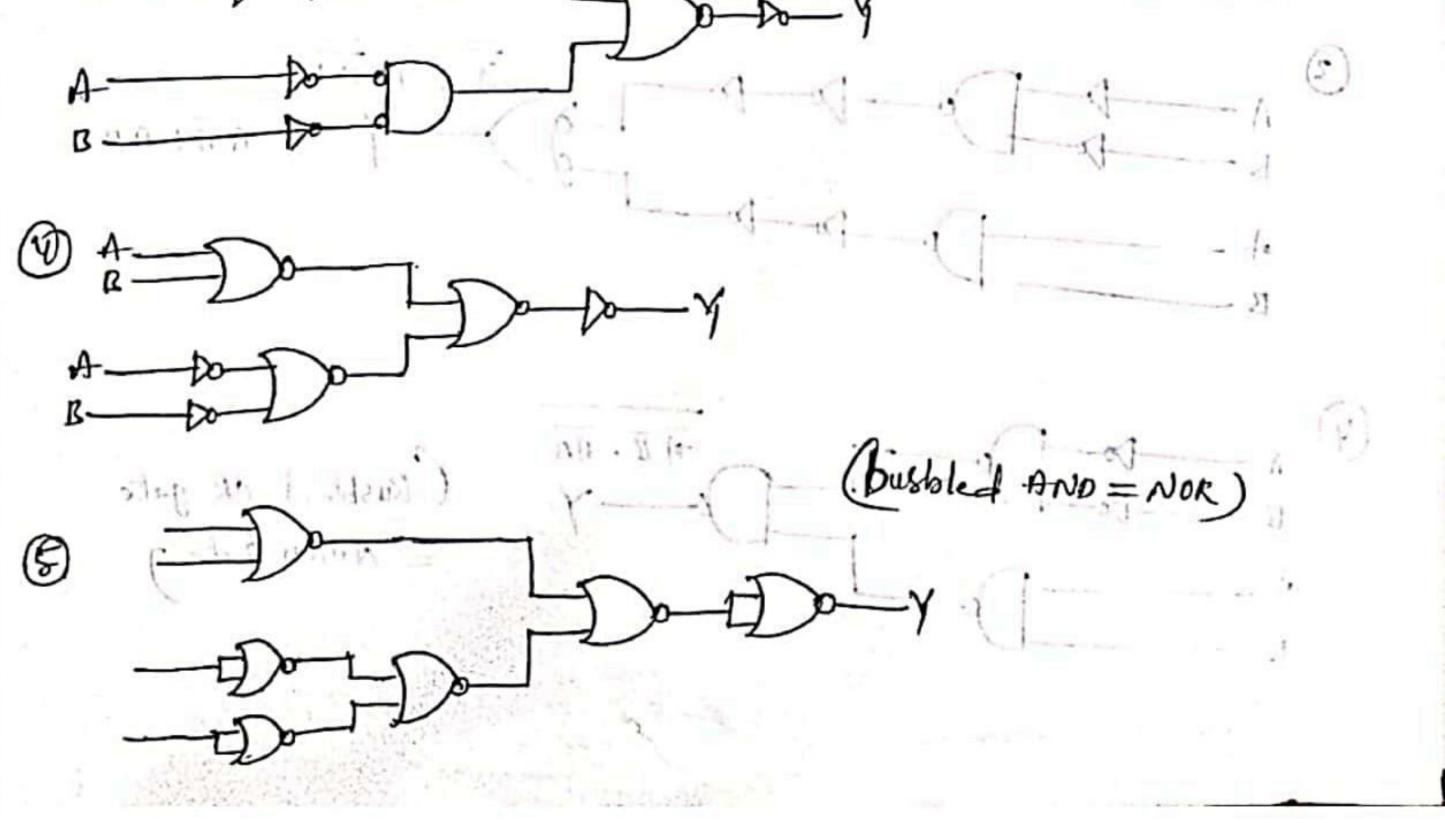

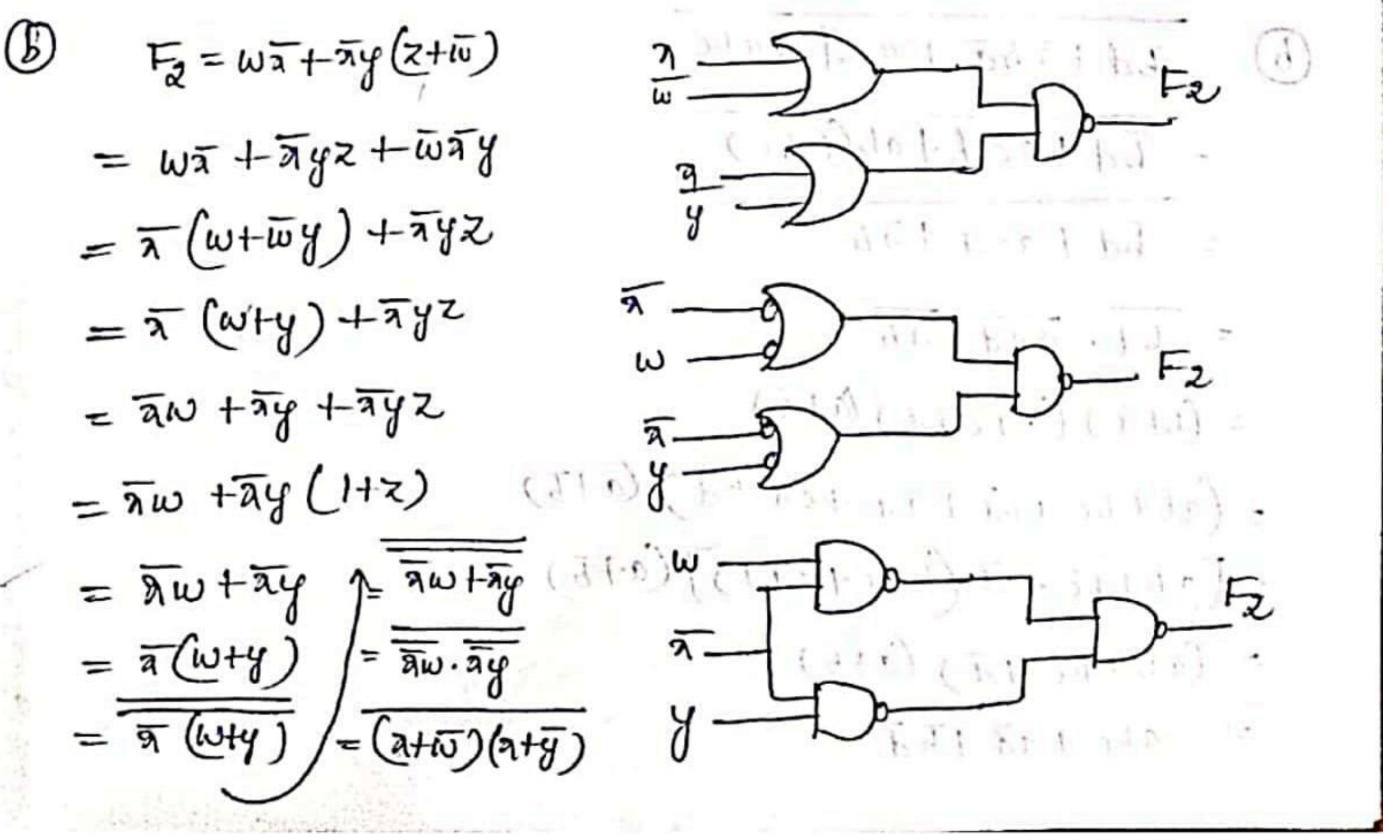

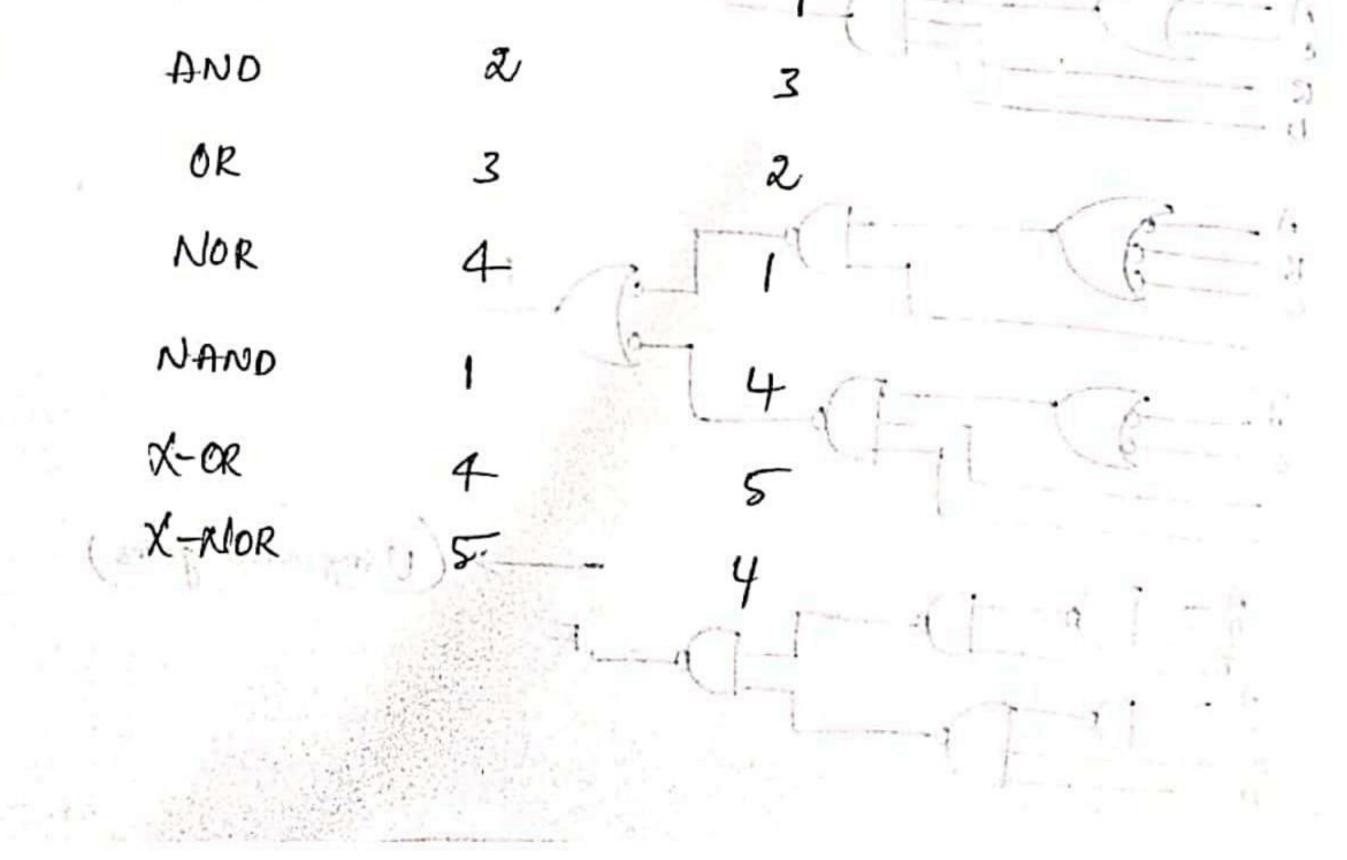

The procedure to convert an AOI logic to NAND logic (or) Alor logic is given below. Draw the exect 10 AOI Logic I IT NAND hardworse is chosen, add a circle at the output q each AND gete and at the inputs to all the OR gates. (3) If NOR hardware & choosen, add a circle at the output q each OR gate and at the inputs to all the AND gates. (9) Add (07) Lubtract an invester on each line that received a circle in step@ (1) 3 that the polarity of signals on those lines remains from that q the original allegram. Replace bubbled or by NAND and bubbled AND by NOR: 5

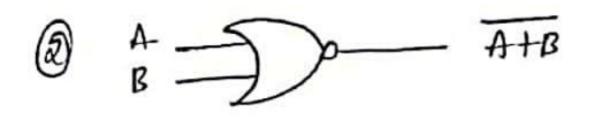

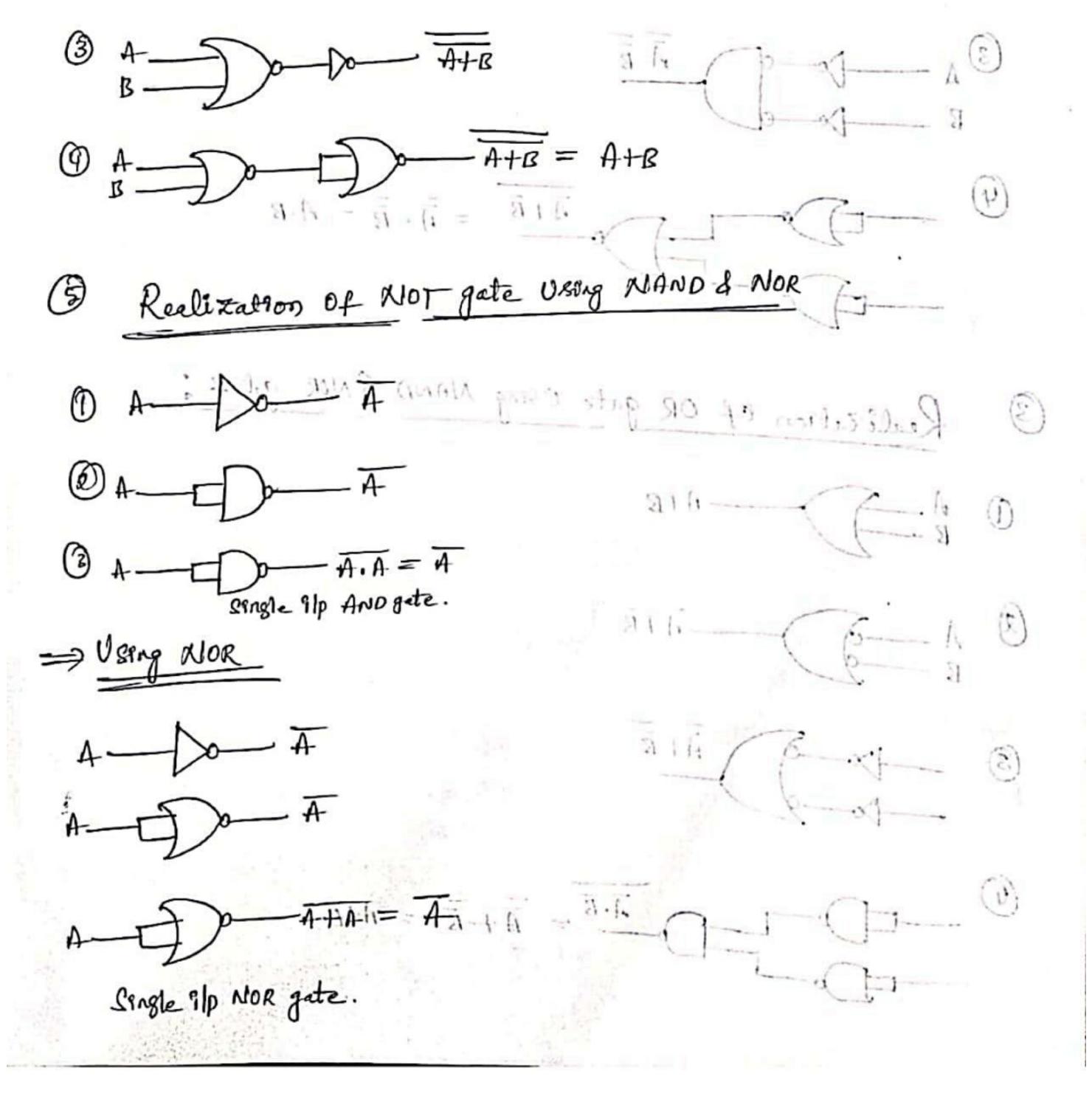

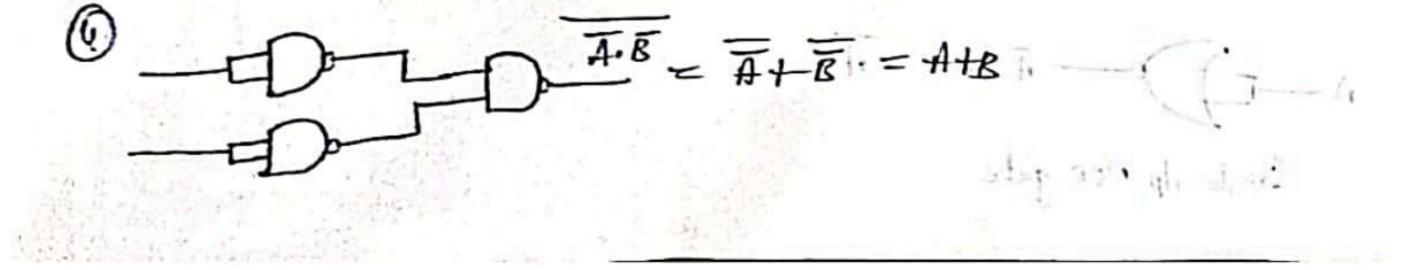

Realization of AND gate Using NOR Gate - ( 125 (2) 1.B ash (= 10) A·B () f=g AB 3 A---- $\overline{\overline{A} + \overline{B}} = \overline{\overline{A}} \cdot \overline{\overline{B}} = \overline{A} \cdot B$ 116 (3) Redits then of Not 112 C Realization of OR gate Using NAND SNOR gates . 1. 1)

S  $(\mathbf{y})$ AtE A+B+A+Bod A B A+R Stikeli 小一日日 Denter ()  $\frac{\partial f}{\partial t} = (A + \overline{B}) + (\overline{A + a})^{0} = (A + \overline{B}) + (\overline{A + a})^{0}$ A.B.L AR +AR 11